# **Digital Guitar Amplifier and Effects Unit**

Shaun Caraway, Matt Evens, and Jan Nevarez Group 5, Senior Design Spring 2014

# **Table of Contents**

| 1.<br>2. |             | ject  | ve Summary                           | 2 |

|----------|-------------|-------|--------------------------------------|---|

|          | 2.2.        | Obj   | ectives                              | 3 |

|          | 2.3.        | Pro   | ject Requirements and Specifications | 3 |

|          | Re:<br>3.1. |       | ch<br>ital Signal Processing         |   |

|          | 3.1         | .1.   | Requirements                         | 1 |

|          | 3.1         | .1.1. | Sampling Rate                        | 1 |

|          | 3.1         | .1.2. | Audio Word Size                      | 5 |

|          | 3.1         | .2.   | Processor Comparison                 | 5 |

|          | 3.1         | .3.   | Features                             | 3 |

|          | 3.1         | .3.1. | Programming Method6                  | 3 |

|          | 3.1         | .3.2. | Real-Time OS                         | 3 |

|          | 3.1         | .3.3. | Ports Available                      | 7 |

|          | 3.2.        | Ana   | ılog7                                | 7 |

|          | 3.2         | .1.   | Input7                               | 7 |

|          | 3.2         | .2.   | Output                               | 3 |

|          | 3.3.        | Dat   | a Converts                           | ) |

|          | 3.3         | .1.   | Analog to Digital Converts           | ) |

|          | 3.3         | .2.   | Digital to Analog Converts           | ) |

| ;        | 3.4.        | Cor   | nmunication11                        | I |

|          | 3.4         | .1.   | UART                                 | I |

|          | 3.4         | .2.   | SPI11                                | I |

|          | 3.4         | .3.   | UPP                                  | 2 |

|          | 3.4         | .4.   | EMIF16                               | 2 |

|          | 3.4         | .5.   | SRIO 12                              | 2 |

|          | 3.4         | .6.   | McBSP                                | 3 |

|          | 3.5.        | Algo  | prithms                              | 3 |

|          | 3.5         | .1.   | K Method14                           | 1 |

|          | 3.5         | .2.   | Newton's Method                      | 5 |

|          | 3.5         | .3.   | DK Method 16                         | 3 |

|          | 3.5         | .4.   | DK Method Equations                  | 3 |

| 3    | 3.5.5.   | Impedance Decomposition       | 17 |

|------|----------|-------------------------------|----|

| 3    | 3.5.6.   | Component Models              | 18 |

| 3    | 3.5.7.   | Vacuum Tube Models            | 18 |

| 3    | 3.5.8.   | Diode Model                   | 20 |

| 3    | 3.5.9.   | Transformer Model             | 20 |

| 3    | 3.5.10.  | Effects Algorithms            | 23 |

| 3    | 3.5.10.1 | Delay                         | 23 |

| 3    | 3.5.10.2 | 2. Reverb                     | 24 |

| 3    | 3.5.10.3 | 3. Chorus                     | 25 |

| 3    | 3.5.10.4 | 4. Compression                | 26 |

| 3    | 3.5.10.5 | 5. Speaker Cabinet Simulation | 27 |

| 3.6  | 6. Prir  | nted Circuit Board            | 29 |

| 3    | 3.6.1.   | Layer Consideration           | 29 |

| 3    | 3.6.2.   | OrCad                         | 30 |

| 3    | 3.6.3.   | Eagle                         | 30 |

| 3    | 3.6.4.   | Upverter                      | 31 |

| 3.7  | 7. Use   | er Interface                  | 31 |

| 3    | 3.7.1.   | On Board                      | 31 |

| 3    | 3.7.1.1. | On Board LCD                  | 31 |

| 3    | 3.7.1.2. | Microcontroller for the LCD   | 32 |

| -    | 3.7.1.3. |                               |    |

| 3    | 3.7.2.   | Computer                      | 33 |

| 3.8  | 3. Pov   | ver Supply                    | 33 |

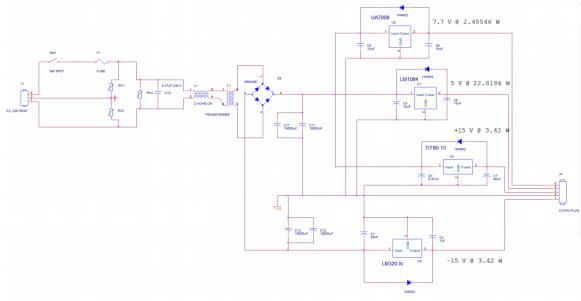

| 3    | 3.8.1.   | Linear Power Supply           | 33 |

| 3    | 3.8.2.   | Switching Power Supply        | 34 |

| 3    | 3.8.3.   | Power Management              | 35 |

| 4. [ | Design   |                               | 37 |

|      |          | tio Inputs and Outputs        |    |

|      | 4.1.1.   | Unbalanced to Balanced Signal |    |

|      | 4.1.2.   | Headphone Output              |    |

|      | 4.1.3.   | Stereo Output                 |    |

|      |          | a Convert Design              |    |

|      | 4.2.1.   | Analog to Digital Converter   |    |

|      | 4.2.2.   | Digital to Analog Convert     |    |

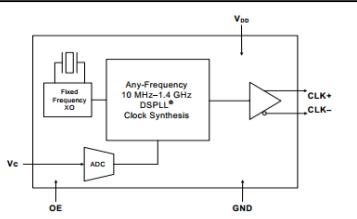

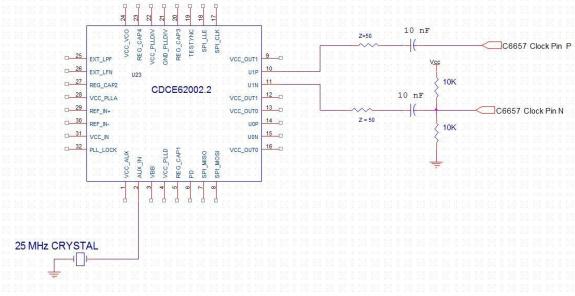

| 4    | 1.2.3.   | Clocking                      | 51 |

| 4  | 4.3. | Digi  | ital Signal Processor                     | 52 |

|----|------|-------|-------------------------------------------|----|

|    | 4.3  | .1.   | Clocking for Processor                    | 52 |

|    | 4.3  | .2.   | Memory                                    | 55 |

|    | 4.3  | .3.   | Power On and Boot Sequence                | 56 |

|    | 4.3  | .4.   | Software                                  | 57 |

| 4  | 4.4. | Use   | er Interface                              | 59 |

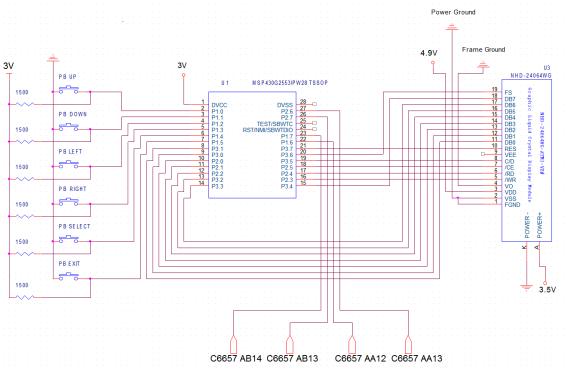

|    | 4.4  | .1.   | Hardware Interface                        | 59 |

|    | 4.4  | .2.   | Software Interface                        | 61 |

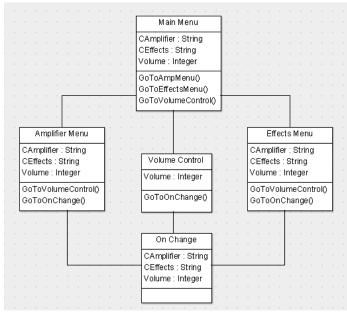

|    | 4.4  | .2.1. | Coding                                    | 62 |

|    | 4.4  | .2.2. | Communication                             | 63 |

| 4  | 4.5. | Prin  | nted Circuit Board Design                 | 64 |

|    | 4.5  | .1.   | Printed Circuit Board Requirements        | 65 |

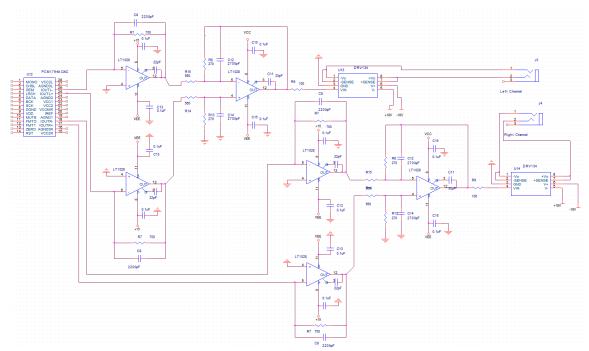

|    | 4.5  | .2.   | Analog Board                              | 65 |

|    | 4.5  | .3.   | Digital Board                             | 65 |

|    | 4.5  | .3.1. | Hardware configuration of the TMS320C6657 | 66 |

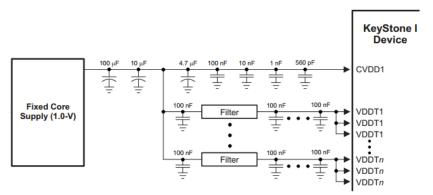

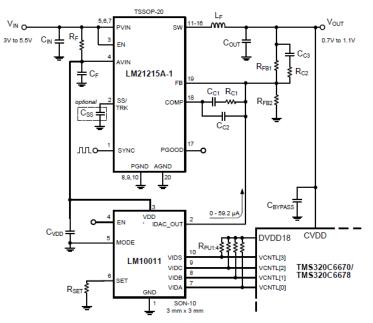

|    | 4.5  | .3.2. | Filtered Voltage Supplies                 | 67 |

|    | 4.5  | .3.3. | DDR3 Routing                              | 69 |

|    | 4.5  | .4.   | Bulk Power Supply Board                   | 69 |

| 4  | 4.6. | Pov   | ver Supply Design                         | 70 |

|    | 4.6  | .1.   | Digital Sub System                        | 72 |

|    | 4.6  | .1.1. | Power On and Off Sequencing               | 75 |

|    | 4.6  | .2.   | User Interface Sub System                 | 75 |

|    | 4.6  | .3.   | Input Output Sub System                   | 75 |

|    | 4.6  | .4.   | Bulk Power Supply                         | 76 |

|    |      |       | Summary                                   |    |

|    | 5.1. |       | dware                                     |    |

| ļ  |      |       | tware                                     |    |

|    | 5.2  |       | DSP                                       |    |

| _  |      |       | User Interface                            |    |

| 6. |      |       | bing<br>tware Algorithms Optimization     |    |

|    |      |       | Testing                                   |    |

|    |      |       | dware Specification Testing               |    |

|    | 7.1  |       | Audio Input                               |    |

|    | 7.1  |       | Analog to Digital Converter               |    |

| 7.1.3.                  | Digital to Analog Converter               | 83      |

|-------------------------|-------------------------------------------|---------|

| 7.1.4.                  | Audio Output                              | 83      |

| 7.1.5.                  | Power Supply                              | 83      |

| 7.1.6.                  | User Interface Hardware Testing           | 85      |

| 7.2. So                 | ftware Algorithm Testing                  | 86      |

| 7.2.1.                  | DSP                                       | 86      |

| 7.2.2.                  | User Interface                            | 88      |

|                         | stration                                  |         |

|                         | estone Discussion                         |         |

|                         | dget and Finance Discussion               |         |

| 9. Append<br>10. Append | dix A – References<br>dix B – Permissions | I<br>II |

# **Figure Listing**

| Figure 1 Circuit Demonstration                                         | 18 |

|------------------------------------------------------------------------|----|

| Figure 2 Triode Simulation                                             | 19 |

| Figure 3 Transformer Model                                             | 21 |

| Figure 4 Gyrator Model                                                 |    |

| Figure 5 Implementation of the Multi-Tap Delay                         | 24 |

| Figure 6 Feedback Network                                              |    |

| Figure 7 Cascade Network                                               | 25 |

| Figure 8 Chorus effect Simulation                                      |    |

| Figure 9 Transfer Function for Compressor                              |    |

| Figure 10 Speaker Cabinet Impulse Network                              |    |

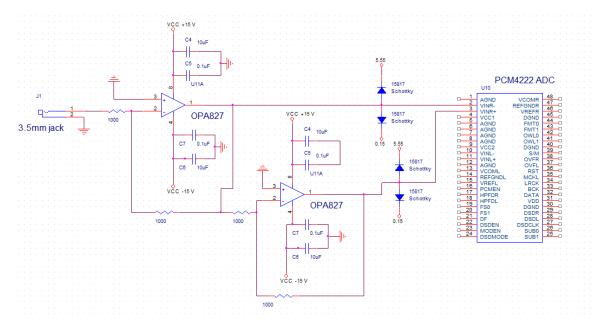

| Figure 11 OPA827 Implementation Schematic                              |    |

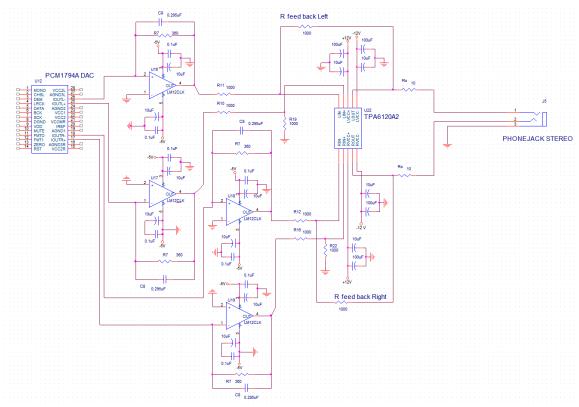

| Figure 12 Implementation of LT1028 as a Current to Voltage Convertor   |    |

| Figure 13 DRV 135 Line Drive Implementation Schematic                  |    |

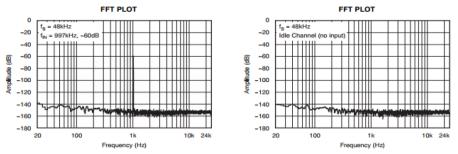

| Figure 14 Frequency Response ADC at 48 kHz                             |    |

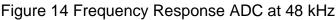

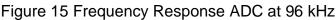

| Figure 15 Frequency Response ADC at 96 kHz                             |    |

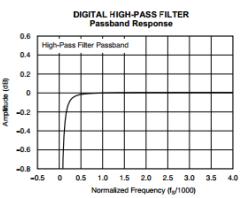

| Figure 16 Bode Plot for High Pass Filter for PCM4222                   |    |

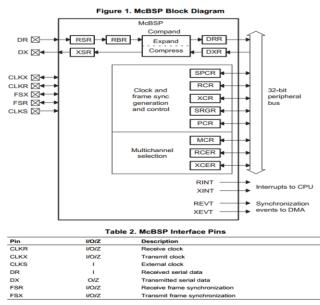

| Figure 17 McBSP Bock Diagram                                           |    |

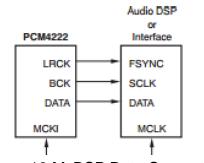

| Figure 18 McBSP Data Converter                                         |    |

| Figure 19 Left-Justified format for the I2 S protocol                  |    |

| Figure 20 Dynamic Range and THD + N                                    |    |

| Figure 21 Signal to Noise Ration and Channel Separation                |    |

| Figure 22 PCM1794A Block Diagram                                       |    |

| Figure 23 System Clock Rates                                           |    |

| Figure 24 Connection Diagram                                           |    |

| Figure 25 Functional Block Diagram                                     |    |

| Figure 26 LVDS Clock Output to CML Buffer                              |    |

| Figure 27 Amplifier Gain Stages                                        | 58 |

| Figure 28 User Interface Schematic                                     |    |

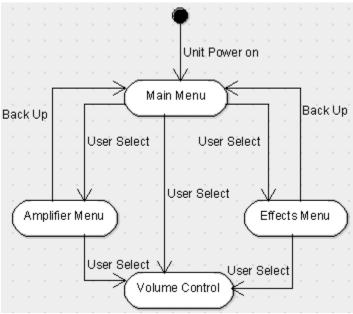

| Figure 29 Menu Flow Chart                                              |    |

| Figure 30 User Interface Class Diagram                                 |    |

| Figure 31 3-Pin SPI                                                    |    |

| Figure 32 Filter Circuit for Filtered Voltage Connection               |    |

| Figure 33 Texas Instruments SmartReflex Class 0 Power Supply for C6657 |    |

| Figure 34 Bulk Power Supply Schematic                                  |    |

| Figure 35 Spring Senior Design 1 Milestone                             |    |

| Figure 36 Summer Senior Design 2 Milestone                             | 89 |

# **Table Listing**

| Table 1 Processor Comparison                                              | 6  |

|---------------------------------------------------------------------------|----|

| Table 2 Line Level Standers for Professional and Consumer Grade Equipment |    |

| Table 3 PCM3168A-Q1 Audio CODEC                                           | 9  |

| Table 4 PCM4222 Audio A/D Converter                                       | 10 |

| Table 5 PCM3168A-Q1 Specifications                                        | 10 |

| Table 6 PCM1794A Specification                                            | 11 |

| Table 7 LCD Screen Comparison                                             |    |

| Table 8 Microcontroller Comparison                                        | 32 |

| Table 9 Power Supply Sequencing                                           |    |

| Table 10 Texas Instruments OPA827                                         |    |

| Table 11 Texas Instruments TPA6120A2 High Fidelity Headphone Amplifier    |    |

| Table 12 Comparison of TINE5534 and LT1028 Operational Amplifiers         |    |

| Table 13 Texas Instruments DRV 135 Audio Balanced Line Driver             |    |

| Table 14 Clock Inputs of C6657                                            |    |

| Table 15 C6657 Clock Jitter Requirements                                  |    |

| Table 16 C6657 Power on Sequence                                          |    |

| Table 17 C6657 Configuration Bits                                         |    |

| Table 18 Pin Assignments of the MSP430G2553IPW28                          |    |

| Table 19 Bit Patter for SPI Communication                                 |    |

| Table 20 Peripherals for the C6657                                        |    |

| Table 21 C6657 Pin Connections for Filtered Voltage Supplies              |    |

| Table 22 Device Power Requirements                                        |    |

| Table 23 Power and Current Requirements for each Supply Voltage           |    |

| Table 24 Supply Voltage Regulators                                        |    |

| Table 25 Power Characteristics of Regulators Utilized by C6657            |    |

| Table 26 Power Requirement for Source Regulators of the Bulk Power Supply |    |

| Table 27 Regulators Implemented on Bulk Power Supply                      |    |

| Table 28 Power Supply Test Loads                                          |    |

| Table 29 Subsystems Voltage Regulators Max Voltage Ratings                |    |

| Table 30 C6657 SPI Logic Voltages                                         |    |

| Table 31 Budget and Cost                                                  | 90 |

# 1. Executive Summary

Guitar amplifiers still utilize vacuum tubes as a means to amplify an electric guitar. Many musicians prefer the sound produced by a vacuum tube amplifier versus a transistor or digital implementation amplifier. When driven into a nonlinear state, vacuum tubes will distort in a gradual way that is pleasing to the ear. By contrast, when a transistor is saturated, it can tend to an overall harsh distortion that is not pleasing to the ear. The quality of the produced sound is the primary advantage of the vacuum tube amplifier over modern transistor amplifiers. However, vacuum tubes are relatively bulky, dissipate a large amount of heat, and are susceptible to becoming microphonic, where the vacuum tubes mechanically vibrate producing undesired sound. Their physical size when compared to transistors is a major disadvantage.

The physical size of a guitar amplifier and complementary audio components is an area ripe for improvement. The speaker cabinet used for these amplifiers is large in size as well as the effects units that complement these amplifiers. The goal is to model and simulate the characteristics of these components in a digital environment in a compact form that allows portability and ease of use. By implementing everything in the digital domain, the user is afforded a more compact, portable solution to their overall system. The digital domain would also allow the user to obtain more amplifier, speaker, and effects modules than would previously be attainable due to size and lack of available capital.

This project wishes to address these issues by creating a standalone device that would simulate vacuum tubes and the amplifiers that utilize them. Furthermore, the project will address a few other issues that arise from the use of these large amplifiers. The unit will also include the speaker cabinet simulations and digital effects that are normally used by musicians. This will reduce the overall cost that a musician would normally incur by investing in every component of a typical guitar rig and allow for far more flexibility than would normally be attainable in the analog domain.

There are products that have similar capabilities as the proposed project. However, the available products are relatively expensive and are difficult to operate. Most of these products utilize a general purpose computer in order to run software for simulating such effects. The problem with this method is that it is a general purpose computer that has its resources divided and is not designed for manipulating floating point numbers at a high rate. Simulating a guitar amplifier circuit in real-time becomes a resource intensive task for the computer to handle. This design will utilize a separate DSP processor in order to simulate the amplifier circuit, speaker cabinet, and effects modules. It will need to run in real time and make the user feel as if they have just plugged their guitar into the amplifier that they have selected. The project will also include a more user-friendly interface than current products on the market by exploring new methods with which the user can interact with the device.

# 2. Project Description

### 2.1. Project Motivation and Goals

When you take a look around at current technology we see advances in many areas of electronics and computer software that were not possible ten years ago. The mindset is to make it smaller, faster, and better. That is the case for most areas of technology, at least for one area: guitar amplifiers. Still stuck in vacuum tube era, guitar amplifiers have not evolved like the rest of the world has. Still requiring a separate heater voltage and current, high plate voltages and large transformers, these devices are completely obsolete. So why are they still present in something such as a guitar amplifier? One reason is the nostalgia that is involved with these devices. Many of the individuals who grew up playing through a big, loud amplifier still prefer those amplifiers because of the way they sound when driven into saturation. There have been attempts to lure these individuals away from these large devices, but they always ended up staying with the vacuum tube amplifiers. Previous attempts failed due to poor design or extreme expense associated with the newer devices. This project hopes to put to rest that digital audio is "sterile" or "cold" sounding and create a new device that can effectively replace the devices of the past.

The previous attempts failed not because solid state devices are incapable of reproducing the sound of the much sought after vacuum tube sound. They failed because the understanding of the newer and older devices were not present in order to accurately reproduce the pleasing sound of a vacuum tube in saturation. The goal of this project is to create a system for musicians that accurately replicates the sound of vacuum tube amplifiers, speaker cabinets, and effects units with great sound quality. A DSP algorithm is only as good as the surrounding circuitry that reproduces the sound. This project will be addressing all aspects of the signal path in order to ensure a high quality audio signal is reproduced from the beginning to the end. This entails proper design and high quality components where it is most critical.

This project looks to replace the current systems that guitarist currently employ, which includes the amplifier, speaker cabinet, and effects unit. This is important because not only are the amplifiers themselves cumbersome, but so is the speaker cabinets necessary to reproduce the sound and any effects units that may be included in the system. Due to the nature of this project, it will be necessary to implement a powerful DSP in order to accurately replicate the typical system that a guitarist would use. This project also needs to make sure that the user can operate the device without much complication or the need for an overly complicated interface. Below is a diagram that shows the signal flow of the DSP based system.

## 2.2. Objectives

This audio digital guitar amplifier and effects unit will be the next big device for the music industry. The main objective, above all, for this project is to create a reliable, high performance unit with the capability of modeling vacuum tube amplifiers and a various range of guitar effects all in the digital world. This project will require a high performance digital signal processor to ensure the highest quality sound in an efficient amount of time. Since the normal human has the capability to notice a lag in sound from the time they play to the time they hear this project must be able to operate and model all amplifier and effects under this time frame. This project must also be portable since most music performers will be using our product in live concert event halls although it will still need to be plugged in to receive power. Also, we want to make sure that users can easily and readily use our product right after they open it out of the box by having an efficiency designed user interface for everybody to easily understand and use. This product will be able to simulate a range of different amplifier boxes made of vacuum tubes as well as effects unit all in a single unit and be attached to a speaker box to play or allow for headphones to play back all new modeled sounds.

### 2.3. Project Requirements and Specifications

The requirements and specifications in this section will be the guidelines for each subsequent design portion of this report. Each requirement and specification listed below will be further expanded upon in their respective sections.

- The device will be a single self-contained unit. This includes user interface, and power supply.

- It will be powered by a wall outlet taking in 220-V at 60-Hz.

- A bulk power supply will be used to create an 18-V DC supply voltage. DC to DC regulation will then be used to power the TMS320C6657 processor, Integrated circuits used for DAC and ADC, user interface and other various features which will require a direct current source.

- The device will simulate both vacuum tube amplifiers

- The device will simulate 4 different guitar effects:

- a. Delay

- b. Reverb

- c. Compression

- d. Chorus

- To prevent noticeable delay from input to output all processing of input signals will be completed in no more than 3 milliseconds.

- The device will take input from an electric guitar in the form of a 1/4 inch mono jack (6.35 mm)

- There will be several outputs on the device.

- a. 1/8 inch (3.5mm) output for headphones.

- b. 1/4 inch (6.35 mm) stereo output.

- To interact with the device an integrated user interface will be provided. This will consist of a LCD graphic module and a set of control nobs and switches or possibly a LCD touch sensitive screen use to implement a user graphical interface.

This project has been entered into the Taxes Instruments Innovation Challenge Design Contest. As a result of this the design will require the use of at least 3 different analog integrated circuits or 2 analog integrated circuits and 1 Texas Instrument processor. To meet these requirements the TMS320C6657 Fixed and Floating-Point Digital Signal Processor, MSP430 micro controller, and PCM4222 2-Channel 24 bit Analog to Digital Converter will be used in the design.

# 3. Research

# 3.1. Digital Signal Processing

### 3.1.1. Requirements

In this section we will discuss the requirements for the performance standards for the system. Our process must satisfy both the sound quality and time constraint from our requirements. These two requirements come from a range of different specifications that we must look into for choosing our process. Above those requirements we must make sure that the process is not only capable, but must also be cost effective, and have great accessibility. The specifications for our processor must include audio sampling rate, and audio word size.

### 3.1.1.1. Sampling Rate

For digital audio processing values are continuously sampled from an analog input single and are stored at certain intervals based of the sampling frequency of the system. Based off the Nyquist sampling theorem we must sample our signal at twice the highest frequency from our device. This will ensure that the signal will be perfectly reconstruction in the digital world for the best sound quality. The sound quality goes up because of the continuity of the reproduced signal. By increasing the sampling frequency the greatest continuity is ensured because the gaps between each stored values goes down. The only issue with a sampling frequency that is to high is the incapability of having a processor to be able to read each value and manipulate it to simulate our different amplifies and effects and send it back out before the next value comes in. For this we must choose a good medium for a frequency to ensure sound quality and time constraints. Since the average human ear has the capability of hearing bandwidths of 20 kHz with some humans being able to hear up to 23 kHz range. To be compliant with Nyquist theorem to sample for human hearing we must be around 44 kHz which is a common frequency band

for low grade audio systems. For our project we will be aiming for high grade performance so we will sample at 96 kHz.

#### 3.1.1.2. Audio Word Size

The bit depth of an audio word determines the resolution of the signal being sampled, processed, and transmitted. The larger the bit depth then the greater the quality of the sample. This also varies directly with the signal-to-noise ratio of the output signal. Also the audio word contains quantization error which is the result of truncations of signal values performed when sampling and recording which compromises the signal integrity before it passes through the system. To reduce this error it is best to raise the number of bits to reduce the possibility for truncating audio words. The most commonly used audio word size is 16 bits which is used for compact discs. With 16 bit audio word size we can get a signal-to-noise ratio of about 96 decibels. For our project we will use an audio word size of 24 bits which will result in a signal-to-noise ratio of about 144 decibels.

#### 3.1.2. Processor Comparison

For our digital guitar amplifier unit we looked at various processors and compared them on three different scales to see which would be best to use for our project. The three different metrics we used to compare the processors are frequency, memory space, and energy consumption. For this project we compared the BF537 Blackfin processor by Analog Devices, TMS320C6657 by Texas Instruments, and the TMS320C6457 also by Texas Instruments.

The table, Table 1 Processor Comparison, below compares the frequency of the three processors. The frequency will tell us how fast each processor can execute each of the instructions. This metric is our top priority in picking our processor because the sampling rate we choose was 96 kHz. So while sampling at 96 kHz we need to make sure that we can process all our data before the next signal as well as to make sure our lag time is under 3 milliseconds. From the table below we can see that the TMS320C6657 is the best processor since it will run at a max frequency of 1250 MHz.

The next metric we will compare is memory space. This is an import metric because with the more memory we have on board the less external memory we will need to add to program on. If we are able to not need any external memory this will speed up our overall unit because we will not need to worry about fetching instructions from memory which can be costly and could affect our ability to meet our time constraints. In Table 1 below we compare the onboard memory for each of the processors. For this comparison we can see there is not much difference between the Blackfin and TMS320C6657 processor.

For the last metric we will use to compare processor is energy consumption. This metric will allow us to see how much over all power we will need to run not only the single processor but as the entire system. We would like to make the most cost effect machine possible so the less energy we consume the less we will need to

spend on the power supply. From Table 1 we can see that the Blackfin processor BF537 uses the least amount of watts.

| Processor   | Frequency<br>(MHz) | Memory Size (K<br>Bytes | Energy<br>(Watts) |

|-------------|--------------------|-------------------------|-------------------|

| BF537       | 600                | 132                     | 0.78              |

| TMS320C6657 | 1250               | 128                     | 3.5               |

| TMS320C6457 | 1200               | 64                      | 1.57              |

| Table 1 Processor Comparisor | Table 1 | Processor | Com | parisor |

|------------------------------|---------|-----------|-----|---------|

|------------------------------|---------|-----------|-----|---------|

After looking at all three of these metrics we decided that we will use the TMS320C6657 processor from Texas Instruments. This decision was made because the TMS320C6657 processor out performance the other two processor in speed. Since our biggest concern is timing this processor helps meet our requirements in being able to sample at a rate of 96 kHz and have less than a 3 millisecond lag time.

#### 3.1.3. Features

#### 3.1.3.1. Programming Method

The development of the signal processing applications for the TMS320C6657 process will take place on a PC. The PC will have Code Composer Studio (CCS) from Texas Instruments which will compile and debug all the code. For the development of our project we will use the TMDSEVM6657LS development board with integrated XDS200 emulator from Elnfochips. This will allow us to code in Code Composer Studio and run in real time and debug our code.

The development board for this project will be running SYS/BIOS Multicore Software Development Kit (MCSDK) from Texas instruments which will be explained more in the Real-Time OS section below. All the code will first be programmed in CCS on the PC and then ported over to the integrated XDS200 emulator through a USB to Serial port using Telnet client commination. This will allows us to interact and run all applications for debugging and test validation. All code for this project will be coded in the C language.

For this project we will need simulate an amplifier with tubes which requires extensive math and matrix multiplication. To help with this the use of MATHLIB from Texas Instruments will help to ensure that all matrix multiplications will be done in the most timely and efficient manner.

#### 3.1.3.2. Real-Time OS

The real-time Operating System (OS) we will use for our processor is the SYS/BIOS from Texas Instrument. This is a real-time scheduling and synchronization tool. This is important for us since our DPS processor has two cores to make sure that we are running all our code properly without having to code our own multithreading synchronization. This real-time OS also helps to minimize memory and CPU requirements whenever it can. For our real-time OS

we can either code in C or C++ through Code Composer Studios (CCS). We have chosen to do all of our coding for this project C. The real-time operating system is able to cut down on memory size because it modularize only the APIs you use and bound all into the executable program as well as eliminating object creation calls. This is good since we only have a limited amount of space on the processor for coding so it's not important to import the entire MATHLIB library but the functions that we actual use and need. The real-time OS also structures support for communication and synchronization between threads with the use of semaphores. This will help us do multiple calculations at once that do not share critical sections and are able to run concurrently to help meet our time constraint for our project off less than 3 ms of lag time.

#### 3.1.3.3. Ports Available

There are several ports available to use with the TMS320C6657 processor. The ports will allow us to interface with all of our external peripheral items. The most import thing is to make sure we can program our processor. We also will need to make sure we can communicate with both the analog to digital converter and digital to analog converter. The next item we will need to communicate with is the user interface. The last item we will have to interface with is external memory. The available ports we have to select from to access each of these different peripheral are: SRIO, PCIe, HyperLink, Gigabit Ethernet, 32-Bit DDR3, 16-Bit EMI, Universal Parallel Port (UPP), UART, McBSP, I2C, and SPI ports. Later in this section we will look at these ports in detail. Since the C6657 processor offers a range of different ports to interface with peripheral items each needs to be analyze to find the best possible to interface port to control the user interface, analog-to-digital convert. And the digital-to-analog converter.

#### 3.2. Analog

#### 3.2.1. Input

The input to the device will be an analog signal in the form of a small alternating current sent from an electric guitar. The guitar generates this signal through the use of a transducer that converts the mechanical vibrations of a guitar string into an alternating current. This is done through the use of a magnetic field generated by the pickups on the guitar. When a musician plays the guitar he or she causes the strings of the guitar to vibrate which in turn moves them within the magnetic field generated by the pickup. This disturbance of the field generates an alternating current which is sent from the guitar to an amplifier. To generate the magnetic field pickups employ two methods active, and passive the former being the most common. Active pickups use batteries to induce a magnetic field while passive versions use a ferrous material surrounded by a coil. There are several materials used in the design of the magnets for passive pickups ranging from ferrous steel to alloys. The most widely used material is an alloy of Aluminum Nickel and Cobalt known as Alnico. Not only does the magnetic material used vary but so does the design and shape of the magnetic core. Pickups commonly use either 6 magnetic pole pieces which are small cylinders, or a solid piece of marital known as a blade. Both of which have a coil of wire wrapped around them. Appling different

combinations of shapes and material have the ability to alter the sound of the guitar. Using pole pieces of Alnico alloy reportedly generates brighter tighter tones, while their steel counterparts produce a loose fatter tone.

Originally pickups were a single coil wrapped around the magnetic material. These early pickups were very susceptible to interference generated by other electronic device and prone to unwanted feedback. However in 1955 Seth Lover ¬an engineer working for Gibson Musical instruments invented a two coil pickup. This two coil pickup became known as the Humbucker, for its ability to remove unwanted hum from the output of the guitar. The Humbucker works by using two coils which are 180 degrees out of phase of each other. This effectively subtracts an unwanted signal such as noise from each other canceling them out.

When designing the analog input to the Digital Guitar Amplifier and Effects Unit there are several things that will be considered. To avoid signal degradation and allow for the greatest maximum voltage to be transmitted from the guitar to the device the input impedance of the device will need to be much greater than that of the guitars output. Traditionally guitars featuring active pickups have very low output impedances generally 100-ohms. While guitars featuring passive pickups have higher output impedances ranging from 6k to 10k-ohms. The device will be designed to receive input from an electric guitar via a 1/4 inch mono jack (6.35 mm) however guitars are not the only device that uses this type of jack. Special considerations in the form of over voltage protection may be implemented to protect the device. This would assure that if an active device sourcing more voltage than the input can handle it will not be damaged. When dealing with audio signals noise always needs to be taken into consideration. To help combat unwanted noise the input signal will be converted from an unbalanced signal to a balanced one allowing for common mode rejection to filter noise that may be introduced throughout the processing of the signal within the device.

#### 3.2.2. Output

The device will be designed to output an analog signal to headphones via a 3.5mm output jack, and audio mixing tables, independently powered speakers such as a public address system via a 1/4 inch (6.35mm). There is a large range of headphones commonly availed on the market which utilizing some form of transducer to create an audible sound from an input signal. The most commonly used transducers in headphones are moving coils and electrostatics. Headphones featuring the electrostatic transducers require a large voltage input ranging from 100-V to 1000-V, can have input impedances reaching up to 170-Kohms, and can easily cost thousands of dollars. Less costly headphones employ mechanical transducers called moving coil drivers. Headphones ranging from cheap 5 dollar ear buds to more expensive 200 dollar consumer grade headphones. The input impedances of these headphones can be as low as 16-ohms. The device will be designed to provide appropriate output for headphones ranging in input impedances of 16 to 60 ohms. This will allow for low cost and consumer grade headphones to be utilized with the device. To interface the headphones with the device a 3.5mm jack will be made available. The device will also feature a volume control for both the stereo and headphone outputs via the user interface. The volume will be adjusted digitally while the signal is being processed by C6657 DSP chip.

The device will provide two channel differential stereo output at line level. Line level is an industry standard for connecting analog audio devices including but not limited to mixing tables, and audio amplifiers. Line level industry standers for professional and consumer grade equipment are listed in the following Table 2

|              | Peak      | Peak to Peak | Nominal    | Nominal |

|--------------|-----------|--------------|------------|---------|

|              | Amplitude | Amplitude    | Level      | Level   |

| Professional | 1.736 V   | 3.472 v      | 1.228 Vrms | +4 dBu  |

| consumer     | 0.447 V   | 0.894 v      | 0.316 Vrms | -10 dBV |

Table 2 Line Level Standers for Professional and Consumer Grade Equipment

Typically the output impedance of audio equipment souring an output at line level ranges from 100 to 600-ohms. While inputs for line level connections feature input impedances greater than 10000 -ohms. The devices output will designed to source a stereo output at a line level capable of interfacing with professional grade equipment. The output impedance of the device will also be designed to fall within the range of 100 to 600 ohms to allow for the maximum voltage transfer to other equipment featuring much larger input impedances.

### 3.3. Data Converts

#### 3.3.1. Analog to Digital Converts

In order to process the incoming guitar signal it will need to be converted to a digital signal. The analog to digital converters will play an important role in the integrity of the overall signal that will be processed. The project will implement high quality converters in order to ensure that the guitar signal coming in is represented with minimal distortion. Due to the desire to have the upmost quality and since there are no real restrictions on overall power draw an audio CODEC will not be implemented in this design. Although CODECs provide a convenient package with low power draw, they do not meet the desired specifications for this project. Below are two tables that compares the very best audio CODEC that TI offers with the very best audio A/D converter that TI offers. Table 3 shows some specifications for the PCM3168A-Q1 audio CODEC (A/D converter). Table 4 shows some specifications for the PCM4222 audio A/D converter.

| SNR           | 107 dB (differential)                                            |

|---------------|------------------------------------------------------------------|

| THD+N         | -93 dB (differential)                                            |

| Channels      | 6                                                                |

| Audio Formats | PCM (Right-Justified, Left-Justified, I <sup>2</sup> C, and TDM) |

| SNR           | 122 dB                                                           |

|---------------|------------------------------------------------------------------|

| THD+N         | -108 dB                                                          |

| Channels      | 2                                                                |

| Audio Formats | PCM (Right-Justified, Left-Justified, I <sup>2</sup> C, and TDM) |

It can be seen that the PCM4222 has better overall dynamic range and SNR. Although the PCM3168A-Q1 has more available channels, this project will only need one channel for the A/D conversion. Both converters output a PCM signal, which will be sent to the DSP as a Left-Justified signal. The PCM4222 is also a hardware controllable device which allows for the use of basic logic switches to control the sampling frequency, HPF, etc. For this project, since the sampling frequency and the mode of operation are going to be static, hardware implementation is all that is required as the need for software control will not be necessary and thus another microcontroller will not be needed.

#### 3.3.2. Digital to Analog Converts

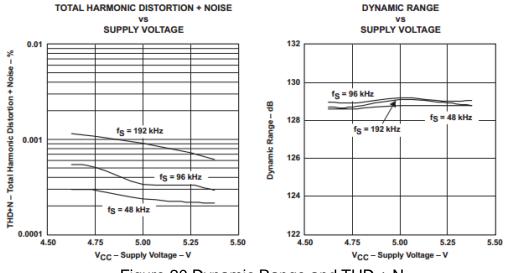

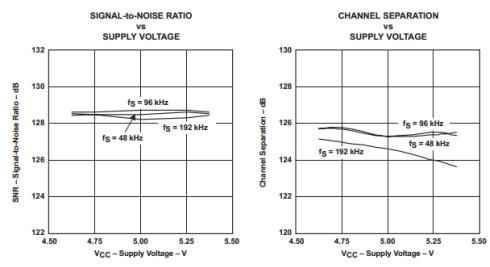

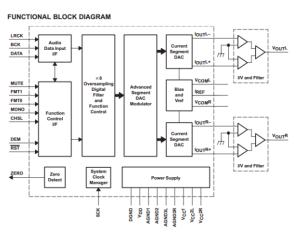

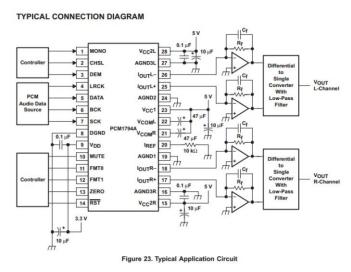

The digital to analog converters for this design play just as much of an important role as the analog to digital converters. The requirements for the digital to analog converters will be to the same standards as to the analog to digital converters. Once again by comparing the PCM3168A-Q1 to a standalone digital to analog converter, there exists a wide disparity in performance. The PCM1794A from Texas Instruments provides excellent performance in a hardware controllable package.

The design will require the need for two of these devices due to the fact that there will be a standard stereo output at line level and a headphone amplifier. Both the headphone amplifier and stereo line driver require two channels of fully differential amplification. The main reason for needing two of these devices is there is a desire to control the volume of the headphone amplifier. The stereo line driver will not need to be controlled as the line out standard dictates that 1.228 V<sub>RMS</sub> be the maximum present signal. In Table 5 and Table 6 show some specifications for the PCM3168A-Q1 and PCM1794A respectively.

| SNR           | 112 dB                                                           |  |

|---------------|------------------------------------------------------------------|--|

| THD+N         | -94 dB                                                           |  |

| Channels      | 8                                                                |  |

| Audio Formats | PCM (Right-Justified, Left-Justified, I <sup>2</sup> C, and TDM) |  |

Table 5 PCM3168A-Q1 Specifications

| SNR           | 127 dB (2V RMS, Stereo)                                          |  |

|---------------|------------------------------------------------------------------|--|

| THD+N         | 0.0004%                                                          |  |

| Channels      | 2                                                                |  |

| Audio Formats | PCM (Right-Justified, Left-Justified, I <sup>2</sup> C, and TDM) |  |

| Table 6 PCM1794A | Specification |

|------------------|---------------|

|------------------|---------------|

It can be seen that the PCM1794A has superior performance when compared to the PCM3168A-Q1 (D/A converter). Although there are advantages to using an audio CODEC with respect to power consumption and controllability, the performance required for this design is not adequate enough. Using separate analog to digital and digital to analog components with their own dedicated external clock will provide the best available performance and thus will offer better overall sonic characteristics.

### 3.4. Communication

#### 3.4.1. UART

The Universal Asynchronous Receiver/Transmitter (UART) peripheral on the TMS320C6657 is a communication port that uses the industry standard TL16C550. This port allows for serial-to-parallel conversion of data to the CPU which will be used to program our processor. The processor can read the UART status at any time as well as be interrupt with the control capability from the UART port. The UART port also allows for a programmable baud which is capable to divide the input clock by divisors from 1 to 65535. The UART on the TMS320C6657 processor also has additional features listed below that might be helpful:

- Choice of 1.8V, 2.5v, 3.3V, or 5V supply

- Single, dual, and quad channel devices available

- Transmit and receive FIFOs of either 16 or 64 Byte depth

- Programmable sleep mode and low-power mode

#### 3.4.2. SPI

The Serial Peripheral Interface (SPI) port on the TMS320C6657 processor is used for high-speed synchronous serial port for input and output bit streaming of lengths 2 to 16 bits. This is done by shifting in and out of the device at a pogrommed bittransfer rate. We can use the SPI peripheral to interface with external I/O or other support compatible devices. This will be useful to us if we would want to control our analog-to-digital converters or an external microcontroller for controlling the user interface. The SPI port on the TMS320C6657 also has additional features listed below that might be helpful:

- 16-bit shift register

- Slave in, master out I/O pin

- Slave out, master in I/O pin

- Multiple slave chip select I/O pins

- Programmable SPI clock frequency range

- Programmable Character length (2 to 16 bits)

- Interrupt capability

- Integrated DMA controller

- Up to 66 MHz operation

3.4.3. UPP

The Universal Parallel Port (uPP) peripheral on the TMS320C6657 processor is used for high-speed parallel interface that has dedicated data lines but minimal control signals. We can use this design to interface with high speed analog-to-digital converters or digital-to-analog converters. This would be good to help with the speed to make sure we cut down time it takes to convert all our signals to allow for more time to analyze and compute our simulation of amplifiers and effects to meet our time constraint for out project. The uPP peripheral also includes an internal DMA controller to help maximize its throughput and help minimizes the overhead to the CPU. We could also use the uPP port to interface with a field-programmable gate array (FPGA) that could be used to help maintain the proper power to the entire system. The uPP port on the TMS320C6657 also has additional features list below that might be helpful:

- Two independent channels with separate data buses

- Channels can operate in same op opposing directions simultaneously

- I/O speeds up to 75 MHz

- 8-16 bit data width per channel

- Internal DMA

- Single and double data rates

- Data interleave mode

#### 3.4.4. EMIF16

The External Memory Interface peripheral on the TMS320C6657 processor which utilizes a 16 bit bus (EMIF16). This bus will be used to interface with all sorts of asynchronous memory devices. The EMIF16 can accesses a total of 256 Mbytes of memory by using four chip selects with each at 64 Mbytes per chip select. This port will allow to for devices like ASRAM, NOR, and NAND memory to be accessed. Unfortunately there are several synchronous memories that the EMIF16 does not support which are DDR1, SDRAM, SDR, and Mobile SDR. This peripheral port ton the C6657 processor will allow for the unit to access more memory since the memory on the processor is very limited. The EMIF16 port also has additional features listed below that might be helpful:

- 8-bit and 16-bit data widths

- Programmable cycle timings for each chip select

- Extended wait support

- Select strobe mode

- Page/Burst mode read support for NOR flash

- Big and little endian operation

3.4.5. SRIO

The Serial Rapid IO (SRIO) peripheral on the TMS320C6657 processor allows for non-proprietary, high-bandwidth, system-level interconnect. It is a packet-switched

interconnect intended primarily as an intrasystem interface for chip-to-chip and board-to-board communications at gigabyte-per-second performance levels. Uses for this architecture can be found to connect microprocessors memory, and memory-mapped I/O devices that operate in networking equipment, memory subsystem, and general-purpose computing. The SRIO line rates supported by the C6657 process device are 1250 Mbps, 2500, Mbps, 3125 Mbps, and 5000 Mbps. The rate scale is used to translate the output of the SRIO PLL to the line rate using the following formula: Line rate Mbps = PLL Output/rate scale. The SRIO port on the C6657 processor also has additional features listed below that might be helpful:

- Flexible system architecture that allows peer-to-peer communication

- Robust communication with error-detections features

- Frequency and port-width scalability

- Operation that is not software intensive

- High-bandwidth interconnect with low overhead

- Low pin count

- Low power

- Low Latency

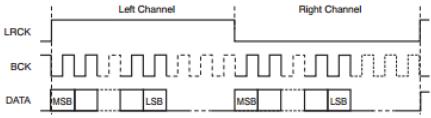

3.4.6. McBSP

The multichannel buffered serial port (McBSP) allows for a direct interface with other Texas Instruments DSPs, codecs, or other devices in system. Since the device will be transmitting and convert audio signals this ports primary use is for audio interface. The two primary audio modes that are supported by the McBSP are the AC97 and the IIS modes. This port may also be used and programmed to support other serial formats but Texas Instrument documentation on the McBSP suggest not if a high-speed interface is needed. The McBSP uses a 32-bit-wide control registers which can be accessible via the internal peripheral bus. This port allows for a data path and a control path to connect external devices. This port will be best used for a project to connect the analog-to-digital converter and the digital-to-analog converters to the C6657 processor. Additional features of the McBSP port that may be helpful are:

- Full-duplex communication

- Double-buffered data register for continuous data stream

- Independent framing and clocking for receive and transmit

- Direct interface to industry-standard codecs

- External shift clock or an internal, programmable frequency shift clock for data transfer

### 3.5. Algorithms

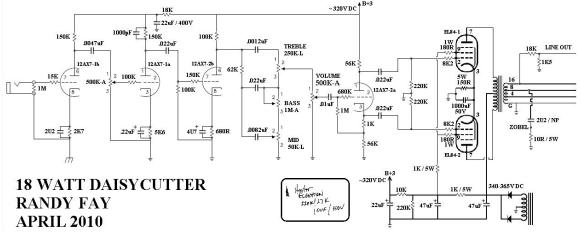

In order to properly simulate a guitar amplifier, the circuit of the amplifier will need to be simulated in order to ensure that the characteristics of the amplifier are properly captured and replicated. There have been many advances in the area of real-time simulation for non-linear systems of differential equations. Our project intends to use the most recent advances in order to ensure that our models are accurate and able to run in real-time. The goal of the simulations is not to capture the exact sound of the amplifier being simulated, but to capture the characteristics and response of every amplifier. The simulations will include the simulation of the power supply, preamplifier, tone stack, and power amplifier circuits. We will ignore the parasitic components that are inherent in passive components as well as layout parasitic such as PCB inductance, resistance, and capacitance. However, parasitic components of active devices and transformer models will be included as these have a far greater effect on the response of the amplifier than the passive and PCB parasitic.

3.5.1. K Method

Due to the fact that the simulation of active devices (specifically vacuum tubes) are inherently non-linear, we are forced to deviate from the traditional state space representation methods typically used to represent this system. Instead we will adopt the DK method developed by David Yeh in order to simulate a non-linear, differential system. The DK method is an automated process that allows us to quickly construct and solve the non-linear differential equations. The derivation is constructed from the K-method which will need to be reviewed before going to the DK method. The equations that describe the K method are below.

$$\dot{x} = Ax + Bu + Ci$$

Equation 1

$i = f(v)$

Equation 2

$v = Dx + Eu + Fi$

Equation 3

Where x is the state of the vector being represented in the system, u is the input, and i is the non-linear function which is a function of v. The non-linear function usually results in an implicit equation and it is necessary to use Newton's Method for solving the implicit equations.

In order to approximate the system, the trapezoidal rule is implemented in the form of the Bilinear Transform to solve the system in the discrete time domain. The discretized state update equation using the Bilinear Transform becomes.

$$\begin{aligned} \mathbf{x}_n &= \mathrm{H}(\alpha \mathrm{I} + \mathrm{A}) \mathbf{x}_{n-1} + \mathrm{HB}(\mathbf{u}_n + \mathbf{u}_{n-1}) + \mathrm{HC}(\mathbf{i}_n + \mathbf{i}_{n-1}) \\ & \text{Equation 4} \end{aligned}$$

Where  $= (\propto I - A)^{-1}$ , I is the identity matrix with the dimensions of A and  $\alpha = 2/T$ . The variable v becomes.

$$v_n = DH((\alpha I + A)x_{n-1} + B(u_n + u_{n-1}) + Ci_{n-1}) + Eu_n + (DHC + F)i_n$$

Equation 5

The function  $v_n$  can be broken up into two terms. One that includes a linear parameter and the other contains the non-linear parameter. They can be represented by the following equations.

$$p_n = DH((\alpha I + A)x_{n-1} + B(u_n + u_{n-1}) + Ci_{n-1}) + Eu_n$$

Equation 6

$$K = DHC + F$$

Equation 7

This results in the implicit function for the non-linear function below

$$i_n = f(p_n + Ki_n)$$

Equation 8

The procedure for solving the system involves solving for  $p_n$ ,  $i_n$ , then update  $x_n$ . After those variables have been solved for the output can be determined based on the system in the general form below.

$$y = A_0 x + B_0 u + C_0 i$$

Equation 9

Where  $A_0$ ,  $B_0$ ,  $C_0$  are the coefficient matrices for the output.

3.5.2. Newton's Method

In order to solve for the implicit equation that exists in  $i_n$ , Newton's method is necessary to solve the system of equations. It was found by Yeh that iterating on voltages results in faster convergence of the solution. It was also found that the use of homotopy is necessary to ensure convergence for large signals (similar to those that will be found in our simulations). The procedure for solving using Newton's method is below.

$$v = Dx + Eu + Ff(v)$$

Equation 10

$$v_n = p_n + Kf(v_n)$$

Equation 11

$$\begin{split} f(v_{it}) &= -v_{it} + p_n + Kf(v_n) \\ & \text{Equation 12} \end{split}$$

Taking the Jacobian of the function  $v_n$  we get.

$$\begin{split} J(v_{it}) &= KJ_F(v_{it}) - I \\ & \text{Equation 13} \end{split}$$

We finally arrive at the final Newton's method equation for solving the voltages of the non-linear functions below.

$v_{it+1} = v_{it} - J(v_{it})^{-1}f(v_{it})$ Equation 14

Homotopy will need to be used to ensure that the initial guess of the system is close enough so that Newton's method converges. Homotopy works by creating a new parameter in the equation in order to create a continuous path from the point where the parameter is equal to zero and when the parameter is equal to one. Below is a general form of homotopy used in conjunction with Newton's method. The initial guess of the system is denoted as  $x^* = 0$ .

$$H(x, \alpha) = F(x) + (\alpha - 1)F(x^*) = 0$$

Equation 15

It will be decided during testing if the use of look-up tables for the non-linear functions is a better choice without losing accuracy and taking up too many resources.

#### 3.5.3. DK Method

Although the K method provides an accurate means for deriving the necessary filters for the simulations, there is not an automated way of creating the equations without rigorous mathematical derivations. David Yeh proposed a method in his thesis that would help automate the process to speed up derivations and to create a more general form of the K method. The method takes advantage of the Modified Nodal Analysis (MNA) in order to create conductance, current source, and voltage node vectors to aid in the derivation. In order to avoid singular matrices, each energy storage component must be constructed into discrete companion circuits. Once this occurs than one can proceed and construct the matrices in order to solve the entire system.

#### 3.5.4. DK Method Equations

The DK method will utilize Modified Nodal Analysis in order to build the system of equations for the simulation. The equation below represents the general form of the system to be solved.

$$\dot{Mx}(t) = f(t, x, u)$$

Equation 16

The matrix **M** will be our conductance vector **G**, **I** will be the current source vector, and **V** is the node voltages and unknown currents. In order to avoid a singular solution in the **M** matrix, a component wise discretization of energy storage elements must be done. The trapezoidal rule is chosen in order to approximate these elements. This will result in a general form for capacitors and inductors below.

$$x[n] = Z(2Gv[n] - x[n-1])$$

Equation 17

Where  $G = \frac{2C}{T}$ , Z = 1 for the capacitor and  $G = \frac{T}{2L}$ , Z = -1 for the inductor. The state is represented by **x** and v[n] is the voltage across the element. By using the same procedure with the K method we arrive at a general form for the state update equation and Newton's Method equations as shown below.

v[n] = Ax[n - 1] + Bu[n] + Ci(v[n])Equation 18 p[n] = Dx[n - 1] + E[u]Equation 19  $f(v_{it}) = -v_{it} + p_n + Ff(v_n)$ Equation 20  $J(v_{it}) = KJ_F(v_{it}) - I$ Equation 21  $v_{it+1} = v_{it} - J(v_{it})^{-1}f(v_{it})$ Equation 22

$A = GA_e + S, B = GB_e, C = GC_e$ , where  $A_e = M^{-1}M_1, B_e = M^{-1}M_2, C_e = M^{-1}M_3$ . The procedure remains the same as the K method with respect to solving for the non-linear, implicit equations.

3.5.5. Impedance Decomposition

One of the drawbacks to using a method such as the DK method or K method is the inherently large matrices that will be constructed in order to simulate the circuits. One method would be to take each stage in a circuit and break it up into blocks to reduce matrix dimensions resulting in faster algorithms. The main drawback of this method is that there is not a clear cut way to accurately simulate the loading affect that each stage would have on previous circuits. Other methods exist for simulating guitar amplifiers, but are either inefficient or focus solely on feed forward circuits.

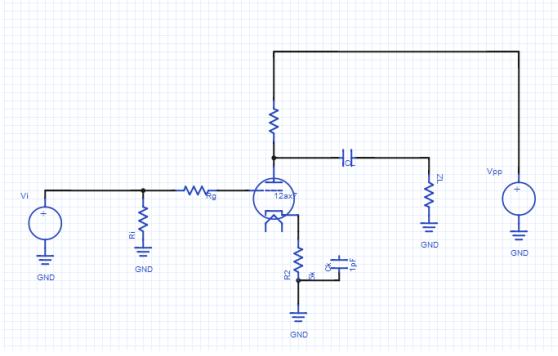

For this project, we propose a method in order to accurately simulate the loading between each stage in order to simplify our matrix dimensions. The Impedance decomposition method takes a stage in any given circuit, say the RC circuit in fig. 1, and adds an arbitrary impedance Z\_L in parallel with the circuit. This will serve as a place holding impedance that represents the input impedance of the connecting circuit. Only one more equation is needed in order to represent the input impedance of the connecting circuit. In the case of the vacuum tube amplifier

circuit in Figure 1 Circuit Demonstration, if another amplifier circuit is connected to the previous amplifier circuit, there exists an instance where there many become an indefinite solution. In this case the user will simply create a special case for the instance of an indefinite solution and continue with the previously derived formula for the input impedance of the connecting circuit. By decomposing the circuits this way, it can be seen that the entire system can be simplified in order to improve matrix operation speeds within the DSP. The only drawback to this method is that it will require the input impedance to be calculated before each state update, but this is more than a fair trade off considering the reduction of matrix dimensions

Figure 1 Circuit Demonstration

#### 3.5.6. Component Models

In order to successfully model an electronic circuit we need to understand the mathematical models for each component. For our passive components we will be taking the ideal component model for a resistor, capacitor, and inductor. Although these components have parasitic components to them, their effect on the entire system response is minimal and we will ignore these for our project. For active devices, we will consider the majority of these parasitic capacitances and inductances as these do have a considerable effect on the system response. We will look at models for the vacuum tubes, diodes and transformers that exist in a common guitar amplifier.

#### 3.5.7. Vacuum Tube Models

The vacuum tubes that will be modelled in our simulations include the 12ax7a, EL84, EL34, and 6L6GC. These are four of the most common models that can be found in many commercially available guitar amplifiers. We will ignore the effect that the heater circuit has on the active devices, as their only contribution is in the

noise floor. For a triode such as the 12ax7a, the equation below developed by Marco Re Cardarilli will be used to simulate the triode.

$$i_{s} = G((V_{gc})(V_{gc} + \frac{V_{ac}}{\mu(V_{gc}, V_{ac})} + h(V_{gc}))^{\frac{3}{2}}$$

Equation 23

$$i_{g} = \frac{i_{s}}{1 + D\frac{V_{ac}}{V_{gc}}^{K}}$$

Equation 24

$$i_{a} = i_{s} - i_{g} = \frac{G((V_{gc})(V_{gc} + \frac{V_{ac}}{\mu(V_{gc})} + h(V_{gc}))^{\frac{3}{2}}}{1 + \frac{1}{D\frac{V_{ac}}{V_{gc}}^{K}}}$$

Equation 25

Equation 25

Where

$$G = \sum_{i=0}^{3} a_i V_{gc}^i$$

$\mu = \sum_{i=0}^{3} b_i V_{gc}^i$   $h = \sum_{i=0}^{3} c_i V_{gc}^i$

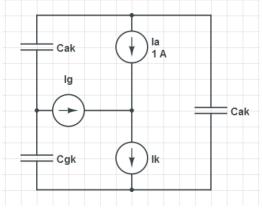

The coefficients a<sub>i</sub>, b<sub>i</sub>, and c<sub>i</sub> are determined through curve fitting of the datasheet to get the best fit. Figure 2 shows the large signal model that will be used for the triode simulation.

Figure 2 Triode Simulation

For the pentode models, which include the 6L6GC, EL34, and EL84 we will be using Koren's vacuum tube model, which is shown in the equations below. The grid current for the pentode can be expressed by the equation below derived by Cohen.

$$I_{a} = E1^{E_{x}} (1 + sgn(E_{1})) \arctan\left(\frac{U_{ak}}{K_{vb}}\right)$$

Equation 26

$$E_1 = \frac{U_{g2k}}{K_p} \log(1 + \exp(K_p \left(\frac{1}{\mu} + \frac{U_{g1k}}{U_{g2k}}\right))$$

Equation 27

$$I_s = \frac{\exp(E_x \log(\frac{U_{g2k}}{\mu} + U_{g1k}))}{K_{g2}}$$

Equation 28

$$I_{g} = \begin{cases} g_{cf} (V_{gk} - g_{co})^{\frac{3}{2}}, & V_{gk} \ge g_{co} \\ 0, & V_{gk} < g_{co} \end{cases}$$

Equation 29

Where  $g_{cf} = 1 \cdot 10^{-5}$  and  $g_{co} = -0.2$ .

3.5.8. Diode Model

For the simulation of the power supply diodes we will use the standard diode equations below.

$$i_D = i_s (\exp\left(\frac{v_D}{nv_t}\right) - 1)$$

Equation 30

Where  $v_D$  is the voltage across the diode, n is the ideality coefficient, and  $v_t$  is the thermal voltage which is about 26mV at room temperature. The diode will model will be necessary for accurate power supply simulation, specifically when simulating ripple voltage across each vacuum tube device. There are also distortion circuits that may become present in some amplifier models that utilize a diode clamping circuit to create distortion in between vacuum tube stages.

#### 3.5.9. Transformer Model

There are a couple of models for the output transformer model that will be considered for the simulation. Below is the ideal transformer model that assumes the linear operating region and no loses due to hysteresis, core saturation, parasitic capacitances, parasitic inductances, and resistances of the windings in the transformer.

$$\frac{V_{s}}{V_{p}} = \frac{N_{s}}{N_{p}} = \frac{i_{p}}{i_{s}}$$

Equation 31

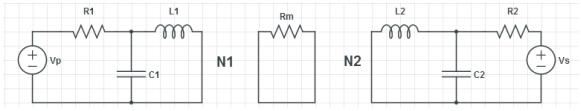

Although this model will give accurate response for the ideal situation while operating in the linear region, the objective of the simulation is to give the most accurate simulation possible to accurately replicate the distortion typically found in guitar amplifiers. Figure 3 shows the transformer model with the parasitic components of the winding, core hysteresis, and core saturation.

Figure 3 Transformer Model

The model in Figure 3 allows the transformer model to be broken up into an electrical and magnetic model. The resistors, capacitors, and inductors can be considered a part of the circuit model instead of the transformer model.

The magnetic core also needs to be modeled in order to accurately model a nonideal, non-linear transformer. The equation below represents the typical relationship in the magnetic core of the transformer.

$$B = \mu H$$

Equation 32

There exists three common models that the magnetic core can be represented as, the Frohlich model and the Jiles-Atherton (JA) model. The Frohlich model can be expressed as:

$$B = \frac{H}{c + b|H|}$$

Equation 33

Where c and b are the parameters that are derived from the material that makes up the transformer core. The JA model can be expressed as

$$B = \mu_0(M + H)$$

Equation 34

Where M is can be derived from the expression:

$$\frac{dH}{dM} = \delta_{M} \frac{M_{an} - M}{k} \operatorname{sign}\left(\frac{dH}{dt}\right) + c \frac{dM_{an}}{dH}$$

Equation 35

$$M_{an} = M_{s} \left( \operatorname{coth}\left(\frac{H + \alpha M}{a}\right) - \frac{a}{H + \alpha M} \right)$$

Equation 36

Where  $M_{an}$ ,  $\alpha$ , a, c, and k are derived from the material properties of the transformer core. When the nonphysical minor loop is going to be generated then  $\delta_{\rm M} = 0$  and when the nonphysical minor loop is not going to be generated  $\delta_{\rm M} = 1$ . The Frohlich model has the advantage of being fairly accurate and less computationally complex. The JA model although is the more accurate model is more robust in terms of computational complexity. This means that the JA model may not be suitable for real-time operation, although the models will be compared during testing procedures to verify if the model is too complex.

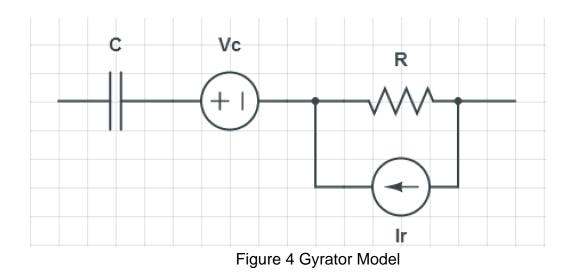

The final model to consider is the gyrator-capacitor model. This model is based on a non-linear capacitor and non-linear resistor. The non-linear capacitor can be expressed as a constant capacitance C in series with a voltage controlled voltage source expressed as:

$$v(v_c) = |av_c|^n sign(v_R)$$

Equation 37

Where  $v_c$  is the controlling voltage over the constant capacitor and A and N are saturation parameters. The non-linear resistor is implemented as a constant resistor R connected in parallel with the voltage controlled current source which can be expressed as:

$$i(v_R) = \left|\frac{bv_R}{R}\right|^n sign(v_R)$$

Where  $v_R$  is the controlling voltage over the constant resistor an b and m are the hysteresis parameters. The main advantage that the gyrator-capacitor has over the Frohlich model is the gyrator-capacitor model will model the hysteresis loop, where the Frohlich model does not model the hysteresis loop. The advantage over the JA model is that the gyrator-capacitor model is more computationally efficient while maintaining good accuracy. The JA model is still more accurate but as stated before requires more computational complexity and could potentially be too robust for real-time simulation. Figure 4 illustrates the equivalent circuit model of the gyrator model.

#### 3.5.10. Effects Algorithms

For guitarist effects are a very integral portion to the sound of the guitar. There are a few common effects that will be modeled which include, delay, reverb, compression, and chorus. Each algorithm will be covered in detail in order to gain a better understanding of what each effect is supposed to do. For this project the complexity of the algorithms will be kept to a minimum as the main purpose is to demonstrate the convenience that the final prototype will have. A finished product would implement slightly more refined and advanced effects. Since the main focus is on the accuracy of the amplifier algorithms and the fact that there are many advanced algorithms implemented in many other products he focus will be to implement simple effects. Although the distortion from the guitar amplifier is technically an effect, this will not be included in this section as the distortion is part of the amplifier circuit.

#### 3.5.10.1. Delay

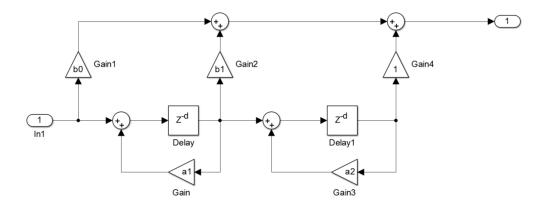

The delay effect is a commonly used effect not just guitars, but also for many other sources including percussion, vocals, etc. The basis of the effect is to delay the incoming signal at a certain frequency and sum the processed audio back into the original signal to create the effect of the source being in a large hall or room. Although there exist many types of delays, this design will focus on the multi-tap delay. One way to implement a multi-tap delay is to implement two delay lines and using feedback to create more reflections. Figure 5 shows the system implementation of the multi-tap delay.

Figure 5 Implementation of the Multi-Tap Delay Changing the delay values will affect the frequency of the delay effect. In Equation 38 is the effect represented in the Z domain.

$$H(z) = b0 + b1 \left(\frac{Z^{-D1}}{1 - a_1 Z^{-D1}}\right) + b2 \left(\frac{Z^{-D1}}{1 - a_1 Z^{-D1}}\right) \left(\frac{Z^{-D2}}{1 - a_2 Z^{-D2}}\right)$$

Equation 38

#### 3.5.10.2. Reverb

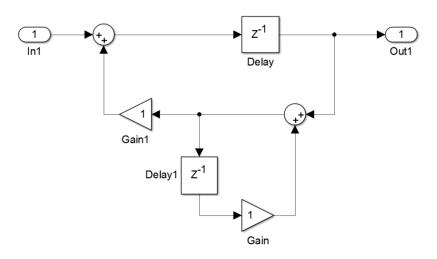

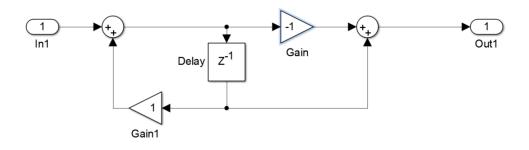

Reverb is another common effect used for guitars to simulate the guitar amplifier being in a large acoustic space. The difference between delay and reverb lies mostly in the complexity and in the design of the delay to produce the effect. Reverb consist of three main components which include the direct sound, early reflections, and late reflections. The reverb that will be implemented in this design will be an algorithm that was designed by M.A Schroeder and James A. Moorer to produce a more realistic reverb. The algorithm is implemented by taking four comb filters with a low pass filter in the feedback network like the one in Figure 6 and sending the final signal to two all pass filters in cascade like the one in Figure 7.

The parallel comb filters will create the echo effect of the reverb. The purpose of the low pass filter in the feedback of the comb filter is to filter out the excess high end that exists within the feedback signal. This allows the high frequency content to be exponentially suppressed allowing for a more realistic sounding reverb. The purpose of the all pass filter is to emphasis the echo effect that the parallel comb filter network has on the incoming signal.

Figure 6 Feedback Network

Figure 7 Cascade Network

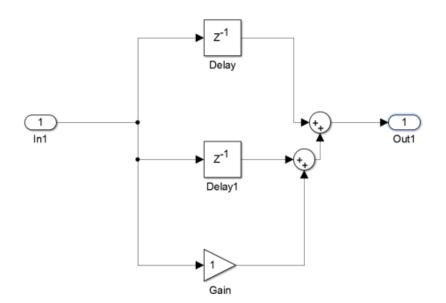

3.5.10.3. Chorus

The chorus effect is a unique effect to the electric guitar as it is used to simulate multiple guitars playing together with a slight delay. When a band plays together, everyone is in sync but there still exist a small amount of delay between every musician that plays together. The chorus effect is designed to simulate this phenomenon and "thicken" the sound of one person playing the guitar to allow for a fuller sound when desired. The basic idea of the algorithm is simple: parallel multiple lines of the same signal and add a variable delay between each line. This in affect creates the "chorusing" sound that can be heard if two or three people playing the same instrument where to play the same piece of music in sync with one another. The low frequency oscillator is used to be able to create the random synchronization offset between each delay line. A frequency between 3 Hz to 5 Hz should suffice in order to create a realistic effect. It is important that the low frequency oscillator is not a predictable oscillator. If the oscillator where predictable than the effect of the chorus would be diminished. Figure 8 shows the basic simulation diagram for the chorus effect simulating three instruments.

Figure 8 Chorus effect Simulation

To implement the chorus using the difference equation derived from the simulation diagram in Figure 8 the expression becomes:

$$y(n) = \frac{1}{3}x(n) + \frac{1}{3}x(n - d_1(n)) + \frac{1}{3}x(n - d_2(n))$$

Equation 39

Where d(n) can be expressed as:

$$d(n) = D(0.5 + LFO(n))$$

Equation 40

The LFO can be implemented using a lookup table or using a DSP on-chip timer.

#### 3.5.10.4. Compression

Dynamics control is an important tool in the audio industry for a couple of reasons. It allows the engineers operating the equipment to better balance the audio to produce a desirable mix to present to the audience and it allows for some creative uses in shaping the tone of an instrument. In the case of a guitar this can help to create longer sustain on notes during solos or a faster attack when playing in genres such as country or jazz. The effect can also be used to help balance some unwanted high frequencies that only occur under dynamic situations. The main idea behind the operation of a compressor is that there exists a threshold with which the user wishes to keep the audio from exceeding. The user can adjust other parameters such as compression ratio, or the ratio for which the audio is reduced with respect to the input. The user can also control the attack time which controls when the compressor is activated and a release time which controls when the compressor is deactivated. All of these parameters will be accessible to the user

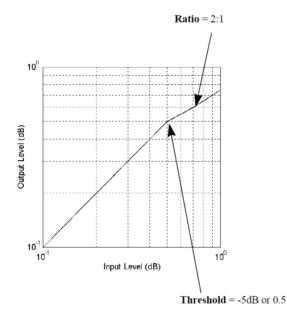

in the design so as to have full control over the function of the compressor. Figure 9 shows the transfer function output of a compressor set to a ratio of 2:1 set at a threshold of -5 dB.

Figure 9 Transfer Function for Compressor

Although the main job of the compressor is to control the dynamics of the system to ensure it does not increase too rapidly, there is a desired amount of harmonics that are added to the signal from being compressed. In most cases this is a subtle amount, but in the case of a guitar effect, it can be taken to more of an extreme to create a more desirable effect.

#### 3.5.10.5. Speaker Cabinet Simulation

One of the most influential components in a guitarist rig is the speaker cabinet. The speaker cabinet plays two significant roles in the overall effect on the sound of the system. One the speaker that is within the speaker cabinet acts as a natural low pass filter to filter out many of the unwanted add high frequency content. When a guitar amplifier is overdriven and operated in a non-linear region the bandwidth is naturally increased and higher frequencies that had less energy now have greater energy in the frequency spectrum. The speaker itself helps to filter out many of these unwanted signals and creates a final and pleasing sound that many musicians have come to know.

There are two types of guitar cabinets that are manufactured and from those two are variants of the two types. The first type is known as an open back cabinet. The design itself is very simple and is chosen for many guitar amplifiers where the amplifier and speaker cabinet are one unit. The open back requires very little attention to detail as there are no parameters needing to be calculated from the speaker to tune the response of both the cabinet and the speaker. The speaker in

an open back design is not sealed. The back of the speaker cabinet is left "open" meaning that there is not a backing on the speaker cabinet. The resulting sound is less directional and more even sounding response. They are used in genres such as jazz and country. The closed back design is the complete opposite of the open back design. The speaker is sealed into the cabinet and a backing exists behind the speaker. The result is a more directional sound with an exaggerated low end response and slight loss in the 1 kHz region of the frequency spectrum. The design becomes more complicated as there is a need to tune the frequency response of the system in order to get the desired output. There is also a need to ensure that the speaker cabinet meets the proper design specifications or the speaker can become damaged. With a sealed back system there are a few variants that these designs will come in. The different sizes include a 1x12, 2x12, and 4x12 cabinet. The first number indicates how many speakers are in the cabinet and the second number indicates the diameter of the speaker cone. These are the most common form factors available on the market today and are considered industry standard. Things such as material used in the speaker cabinet and guality of the speaker component are areas that can affect the tone of the audio signal, but these will not be discussed as there are too many variables too account for.

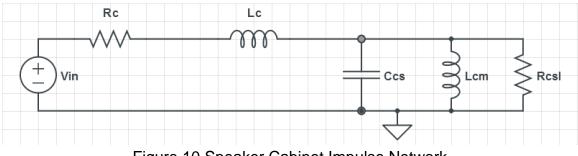

As far as the simulation is concerned, there exists a method by convolution on an impulse response in order to simulate these speaker cabinets. These impulse response are created using the actual physical speaker cabinets and their impulse responses are captured and recorded. Once the data has been collected on the speaker cabinet, the file can then be loaded into a convolver in order to recreate the sound of the speaker cabinet with whatever signal is passed through. The dynamic response of the speaker cabinet is not captured though and will need to be modeled in order to get the full effect of the speaker cabinet impulse response. In Figure 10 the equivalent electrical circuit is shown that would be attached to the actual circuit simulation.

Figure 10 Speaker Cabinet Impulse Network