# EEL 4783: HDL in Digital System Design

#### Lecture 3: Logic Design with Behavioral Models

Prof. Mingjie Lin

**Stands For Opportunity**

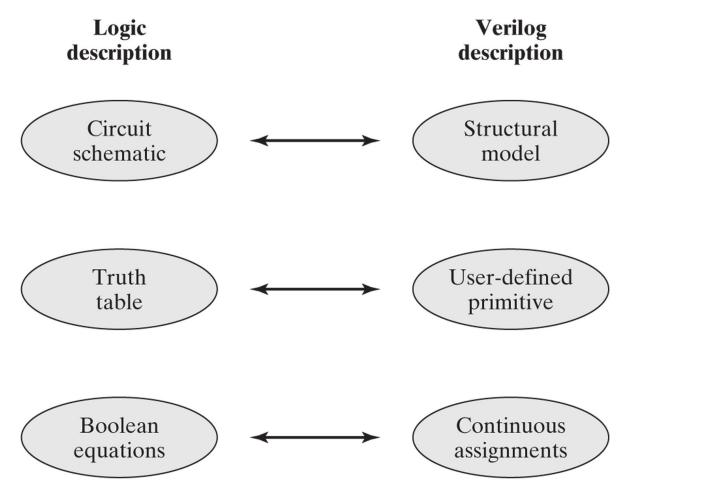

#### **HDL Levels**

Copyright © 2011 Pearson Education, Inc. publishing as Prentice Hall

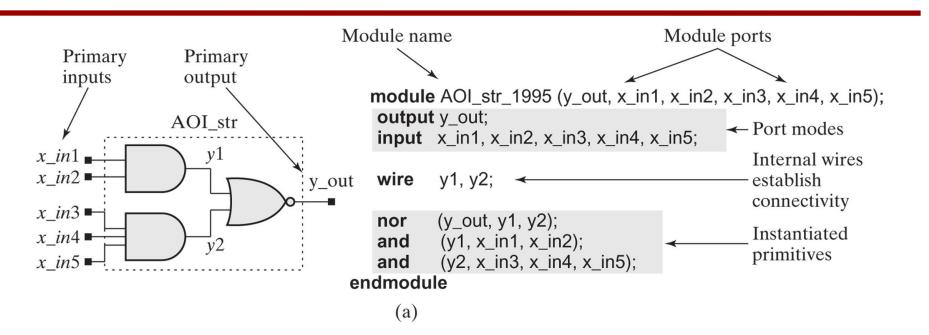

# An AOI Circuit

**module** AOI\_str\_2005 (**output** y\_out, **input** x\_in1, x\_in2, x\_in3, x\_in4, x\_in5); **wire** y1, y2;

```

nor (y_out, y1, y2);

and (y1, x_in1, x_in2);

and (y2, x_in3, x_in4, x_in5);

endmodule

```

(b)

#### **Behavior Descriptions**

module AOI\_5\_CA0 (y\_out, x\_in1, x\_in2, x\_in3, x\_in4, x\_in5);

input x\_in1, x\_in2, x\_in3, x\_in4, x\_in5;

output y\_out;

assign y\_out = ~((x\_in1 & x\_in2) | (x\_in3 & x\_in4 & x\_in5));

endmodule

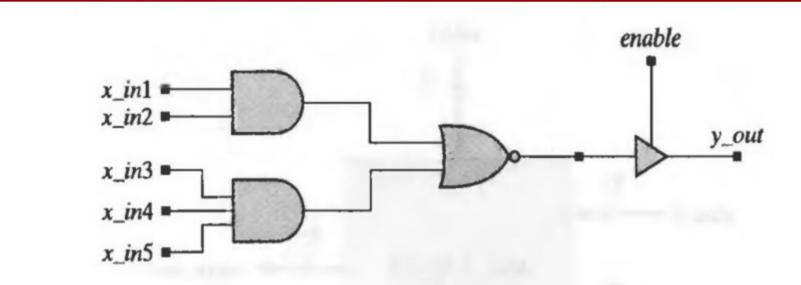

# **Modified AOI**

module AOI\_5\_CA2 (y\_out, x\_in1, x\_in2, x\_in3, x\_in4, x\_in5, enable);inputx\_in1, x\_in2, x\_in3, x\_in4, x\_in5, enable;outputy\_out;

wire y\_out = enable ? ~((x\_in1 & x\_in2) | (x\_in3 & x\_in4 & x\_in5)) : 1'bz; endmodule

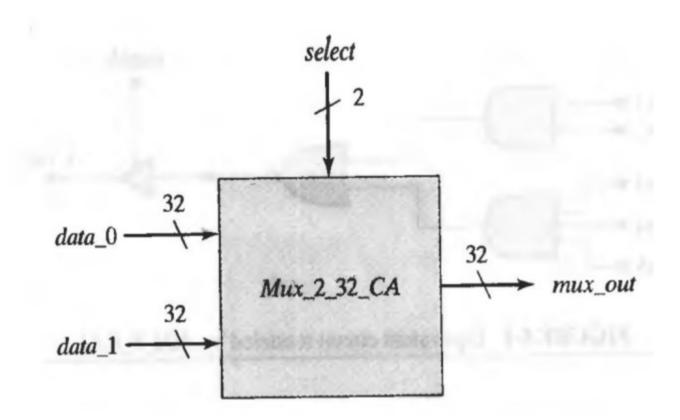

#### 32-Bit Two-Channel MUX

#### 32-Bit Two-Channel MUX

module Mux\_2\_32\_CA ( mux\_out, data\_1, data\_0, select);parameterword\_size = 32;output[word\_size -1: 0]mux\_out;input[word\_size -1: 0]data\_1, data\_0;select;

assign mux\_out = select ? data\_1 : data\_0; endmodule

# **Propagation Delay**

```

module AOI_5_CA3 (y_out, x_in1, x_in2, x_in3, x_in4);inputx_in1, x_in2, x_in3, x_in4;outputy_out;wire #1 y1 = x_in1 & x_in2;// Bitwise and operationwire #1 y2 = x_in3 & x_in_4;// Complement the result of bitwise OR operationendmodule

```

# **Continuous Assignments**

```

module compare _2_CA0 (A_lt_B, A_gt_B, A_eq_B, A1, A0, B1, B0);

input A1, A0, B1, B0;

output A_lt_B, A_gt_B, A_eq_B;

assign A_lt_B = (~A1) & B1 | (~A1) & (~A0) & B0 | (~A0) & B1 & B0;

assign A_gt_B = A1 & (~B1) | A0 & (~B1) & (~B0) | A1 & A0 & (~B0);

assign A_eq_B = (~A1) & (~A0) & (~B1) & (~B0) | (~A1) & A0 & (~B1) & B0

| A1 & A0 & B1 & B0 | A1 & (~A0) & B1 & (~B0);

endmodule

```

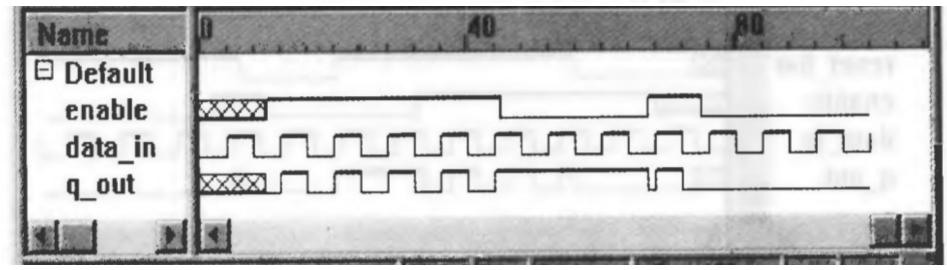

#### Latches and Level-Sensitive Circuits

```

assign q = set ~& qbar;

assign qbar = rst ~& q;

module Latch_CA (q_out, data_in, enable);

output q_out;

input data_in, enable;

assign q_out = enable ? data_in : q_out;

endmodule

```

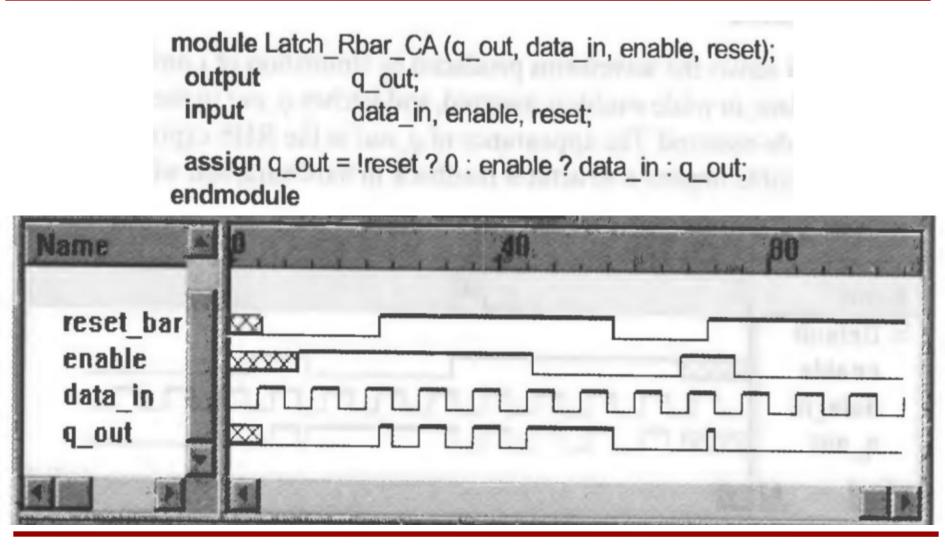

## More Complex Latch

# **Cyclic Behavior of Flip-Flops**

```

module df_behav (q, q_bar, data, set, reset, clk);inputdata, set, clk, reset;outputq, q_bar;regq;

```

```

assign q_bar = ~ q;

```

always @ (posedge clk) // Flip-flop with synchronous set/reset

```

begin

if (reset == 0) q <= 0;

else if (set ==0) q <= 1;

else q <= data;

end

endmodule</pre>

```

## Even More Complex FFs

| module asyn         | ch_df_behav (q, c  | _bar, data, set, clk, reset );                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| input               | data, set, rese    | t, clk;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| output              | q, q_bar;          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| reg                 | q;                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| assign              | q_bar = ~q;        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| always @ (<br>begin | negedge set or n   | egedge reset or posedge clk)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| if (reset =         | == 0) q <= 0;      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| else if             | (set == 0) q <= 1; |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| else q <= data;     |                    | // synchronized activity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| end                 |                    | and a first some of the second s |

| endmodule           |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# Latch vs.Flip-Flop

module tr\_latch (q\_out, enable, data);

output q\_out;

input enable, data;

reg q\_out;

always @ (enable or data)

begin

if (enable) q\_out = data;

end

endmodule

module df\_behav (q, q\_bar, data, set, reset, clk);

input data, set, clk, reset;

output q, q\_bar;

reg q;

assign q\_bar = ~ q;

always @ (posedge clk) // Flip-flop with synchronous set/reset

begin

if (reset == 0) q <= 0;

else if (set ==0) q <= 1;

else q <= data;

ord</pre>

end endmodule

#### **Final issues**

- Please fill out the student info sheet before leaving

- Come by my office hours (right after class)

- Any questions or concerns?