## EEL 4783: HDL in Digital System Design

Lecture 4: Logic Design with Behavioral Models (cont.)

Prof. Mingjie Lin

#### Latch vs.Flip-Flop

```

module tr_latch (q_out, enable, data);

module df behav (q, q_bar, data, set, reset, clk);

data, set, clk, reset;

input

output q out;

output

q, q bar;

input enable, data;

reg

reg q out;

assign q bar = ~ q;

always @ (enable or data)

always @ (posedge clk) // Flip-flop with synchronous set/reset

begin

if (enable) q out = data;

begin

end

if (reset == 0) q <= 0:

else if (set ==0) q <= 1;

endmodule

else q <= data;

end

```

endmodule

# Different Styles of Behavioral Modeling

- Continuous Assignment Model

- Data-Flow/RTL Model

- Algorithm-Based Model

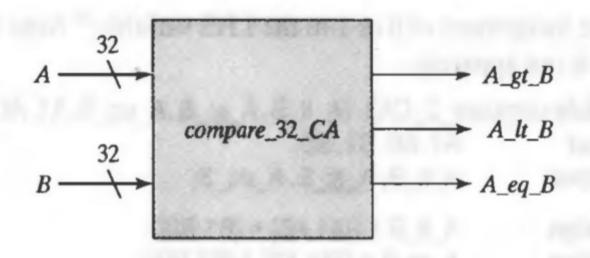

## **Continuous Assignment Models**

# **Continuous Assignment Models**

```

module compare_32_CA (A_gt_B, A_lt_B, A_eq_B, A, B);

parameter word_size = 32;

input [word_size-1: 0] A, B;

output A_gt_B, A_lt_B, A_eq_B;

assign A_gt_B = (A > B), // Note: list of multiple assignments

A_lt_B = (A < B),

A_eq_B = (A == B);

```

endmodule

#### Data-Flow/RTL Models

# Blocking vs. Non-Blocking Statements

- A=B;

- A<=B;

- assign A = B;

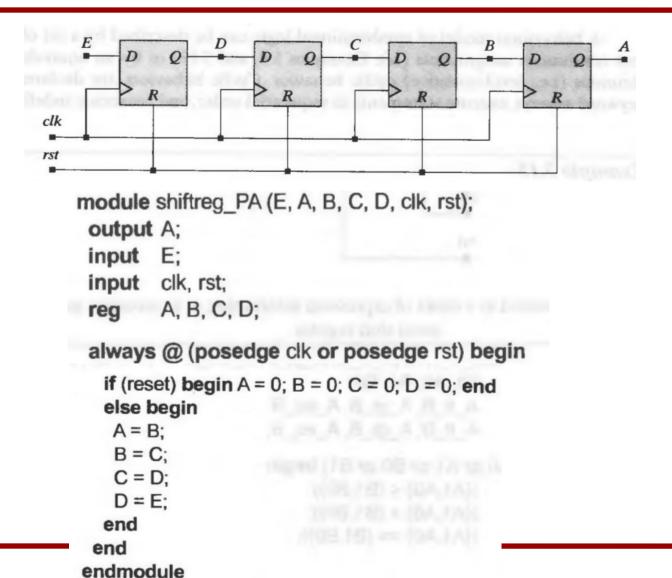

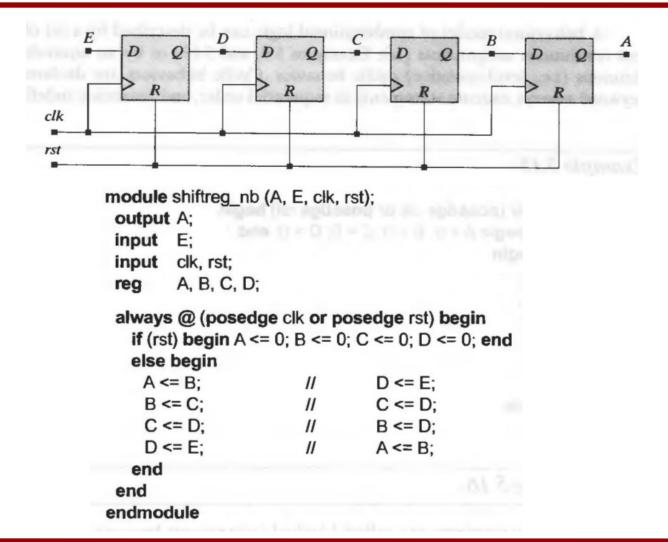

## 4-Bit Shift Register

#### 4-Bit Shift Register

#### **Algorithm-Based Model**

```

module compare_2_algo (A_lt_B, A_gt_B, A_eq_B, A, B);

output A_lt_B, A_gt_B, A_eq_B;

input [1: 0] A, B;

A_lt_B, A_gt_B, A_eq_B;

reg

always @ (A or B)

// Level-sensitive behavior

begin

A It B = 0;

A gt B = 0;

A eq B = 0;

if(A == B)

A_eq B = 1;

// Note: parentheses are required

else if (A > B)

A gt B = 1;

else

A It B = 1;

end

endmodule

```

#### **Behavior Models of MUX**

```

module Mux_4_32_case

(mux_out, data_3, data_2, data_1, data_0, select, enable);

output

[31: 0] mux out;

input

[31: 0] data_3, data_2, data_1, data_0;

[1: 0]

input

select;

input

enable:

[31: 0] mux_int;

assign mux_out = enable ? mux_int : 32'bz;

always @ (data_3 or data_2 or data_1 or data_0 or select)

case (select)

0:

mux int = data 0;

mux_int = data_1;

mux int = data 2;

mux_int = data_3;

default:

mux int = 32'bx;

// May execute in simulation

endcase

endmodule

```

## Behavior Models of MUX (cont.)

```

module Mux 4 32 if

(mux_out, data_3, data_2, data_1, data_0, select, enable);

output [31: 0] mux out;

input [31: 0] data_3, data_2, data_1, data_0;

input [1:0] select;

input

enable;

[31: 0] mux int;

reg

assign mux_out = enable ? mux_int : 32'bz;

always @ (data_3 or data_2 or data_1 or data_0 or select)

if (select == 0) mux_int = data_0; else

if (select == 1) mux_int = data_1; else

if (select == 2) mux int = data_2; else

if (select == 3) mux_int = data_3; else mux_int = 32'bx;

endmodule

```

## Behavior Models of MUX (cont.)

```

module Mux_4_32_CA (mux_out, data_3, data_2, data_1, data_0, select, enable);

output [31: 0] mux out;

input [31: 0] data_3, data_2, data_1, data_0;

input [1:0] select;

input

enable:

[31: 0] mux int;

wire

assign mux_out = enable ? mux_int : 32'bz;

assign mux_int = (select == 0) ? data_0 :

(select == 1) ? data 1:

(select == 2) ? data 2:

(select == 3) ? data 3: 32'bx;

endmodule

```

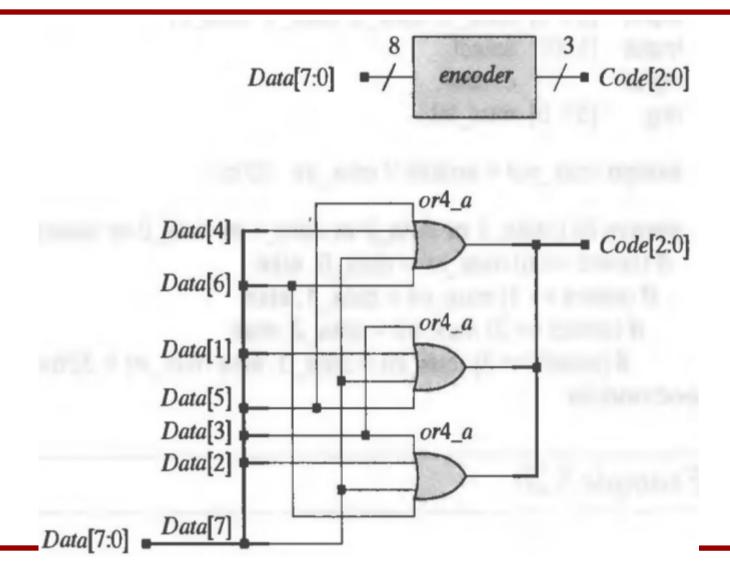

#### **Encoder**

#### **Encoder**

```

module encoder (Code, Data);

[2: 0] Code;

output

input

[7: 0] Data;

[2: 0] Code;

reg

always @ (Data)

begin

if (Data == 8'b00000001) Code = 0; else

if (Data == 8'b00000010) Code = 1; else

if (Data == 8'b00000100) Code = 2; else

if (Data == 8'b00001000) Code = 3; else

if (Data == 8'b00010000) Code = 4; else

if (Data == 8'b00100000) Code = 5; else

if (Data == 8'b01000000) Code = 6; else

if (Data == 8'b10000000) Code = 7; else Code = 3'bx;

end

```

#### **Encoder**

```

always @ (Data)

case (Data)

8'b00000001 : Code = 0;

8'b00000010 : Code = 1;

8'b00000100 : Code = 2;

8'b00001000 : Code = 3;

8'b00010000 : Code = 4;

8'b00100000 : Code = 5;

8'b01000000 : Code = 6;

8'b10000000 : Code = 7;

: Code = 3'bx;

default

endcase

endmodule

```

#### Final issues

- Please fill out the student info sheet before leaving

- Come by my office hours (right after class)

- Any questions or concerns?