# Rapid Prototyping of Wireless Physical Layer Modules Using Flexible Software/Hardware Design Flow

James Chacko jjc652@drexel.edu

Cem Sahin cs486@drexel.edu

Doug Pfeil dsp36@drexel.edu

Dr. Nagarajan Kandasamy kandasamy@drexel.edu

Dr. Kapil Dandekar dandekar@drexel.edu

wireless.ece.drexel.edu

Funded by NSF Grants CNS-0854946, CNS-0923003 & CNS-1422964

# Software Defined Radio (SDR)

#### Characteristics

- Software implementation

- Hardware frontends

## Advantages

- Easily modified

- Faster time to market

Software

**D**efined

**C**ommunication Testbed

- Disadvantages

- Slower speed compared to ASIC

- Hard to achieve real-time operations

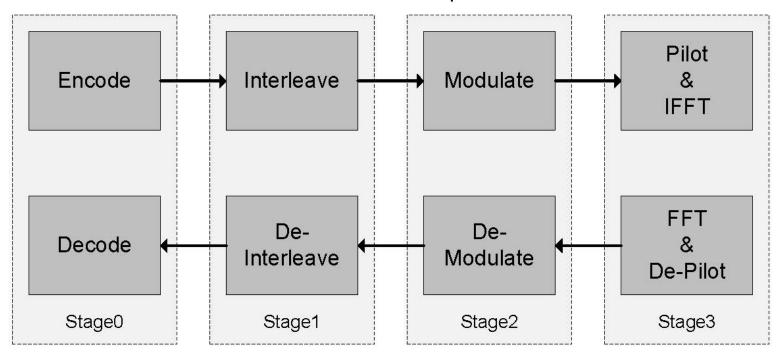

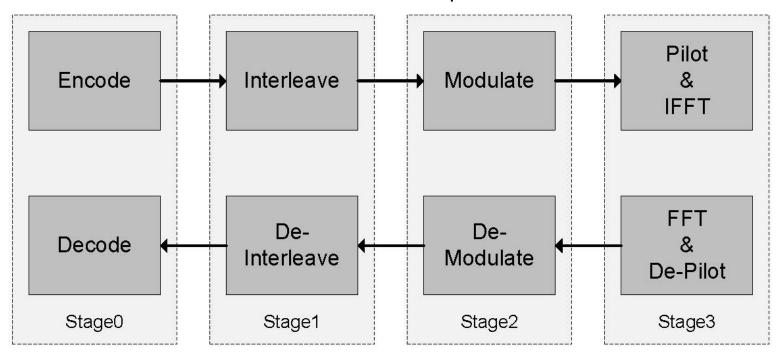

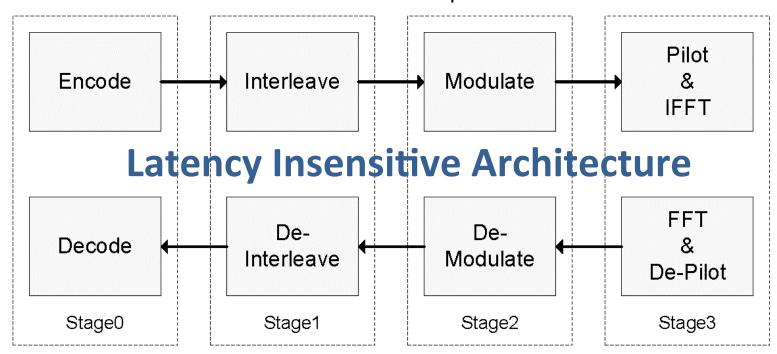

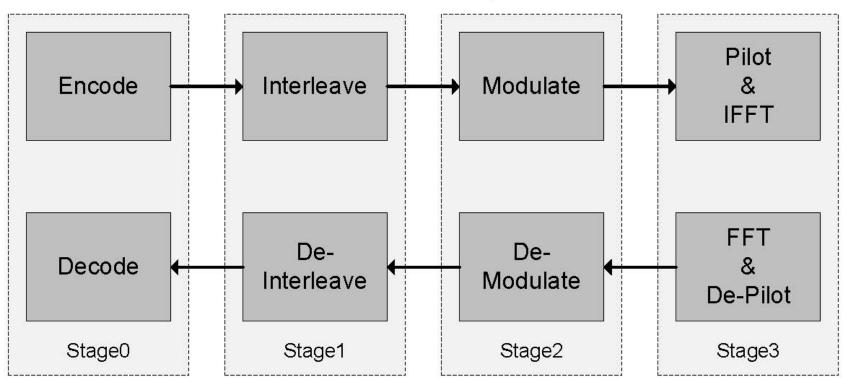

## Generic OFDM Baseband Pipeline

#### Transmit Pipeline

Receive Pipeline

# **Configuration Parameters**

[2,3,4]

| Standard     | Encoder Rates            | Modulation Schemes             | IFFT Size               |

|--------------|--------------------------|--------------------------------|-------------------------|

| 802.16 WiMAX | 1/2 , 2/3 , 3/4 ,<br>5/6 | BPSK, 4-QAM,<br>16-QAM, 64-QAM | 128, 512,<br>1024, 2048 |

| 802.11n WLAN | 1/2 , 2/3 , 3/4 ,<br>5/6 | BPSK, 4-QAM,<br>16-QAM, 64-QAM | 64                      |

| 802.11a WLAN | 1/2 , 2/3 , 3/4          | BPSK, 4-QAM,<br>16-QAM         | 64                      |

| Pipeline Stage | Parameters                               |

|----------------|------------------------------------------|

| Encoder        | Coding rate, Polynomial                  |

| Modulation     | Modulation scheme, Data mapping value    |

| Piloting       | Pilot position, Pilot value, Symbol size |

| IFFT           | Symbol size, Guard prefix                |

## Generic OFDM Baseband Pipeline

#### Transmit Pipeline

Receive Pipeline

- Fixed PHY implementation

- Fixed Configurations

- Fixed rates

## Generic Scalable OFDM Baseband Pipeline

#### Transmit Pipeline

Receive Pipeline

- Fixed- Scalable PHY implementation

- Fixed- Scalable Configurations

- Fixed- Scalable rates

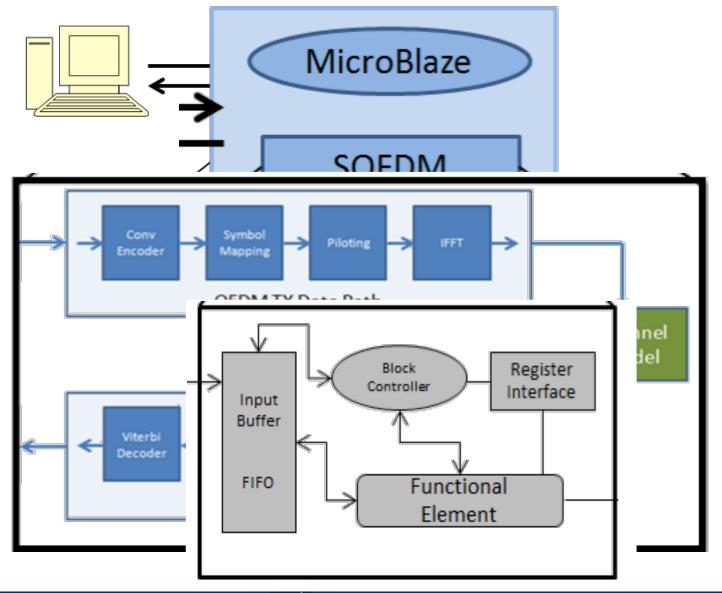

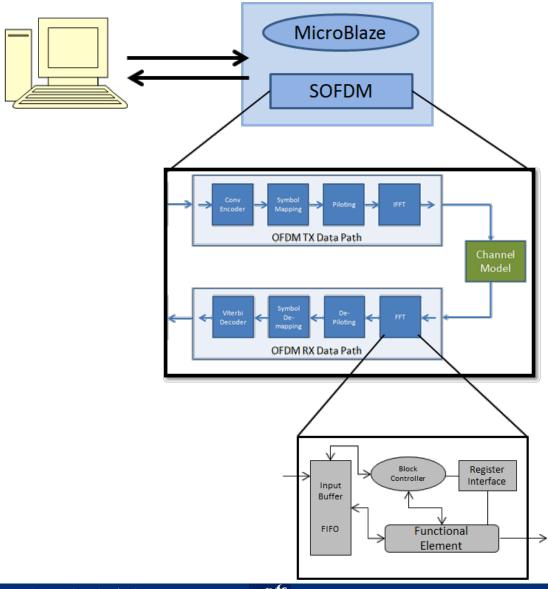

# Software Defined Communication Testbod<sup>[1]</sup>

- Software interface driven flexible hardware implementation

- Software flexibility

- Hardware speeds

- Rapid prototyping

- OFDM based comm. standards

- Variations within comm. standards

- Runtime adaptable

wireless.ece.drexel.edu/sdc

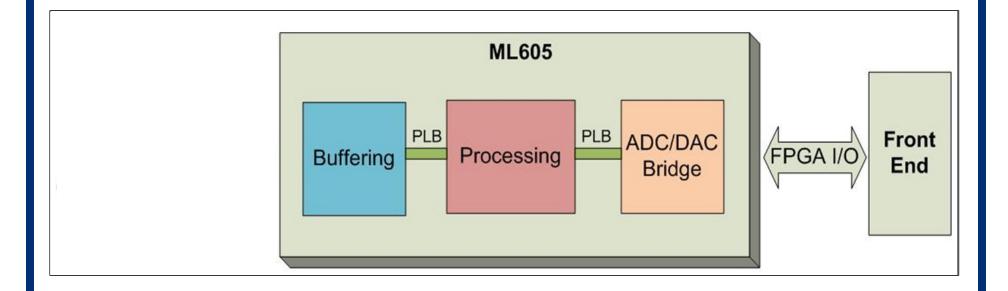

### Hardware Platform

**ML605 Virtex-6 FPGA Baseband**

- 240k logic cells, 700 DSP slices, 400 BRAMs

- Gigabit Ethernet

- FPGA Mezzanine Connector (FMC)

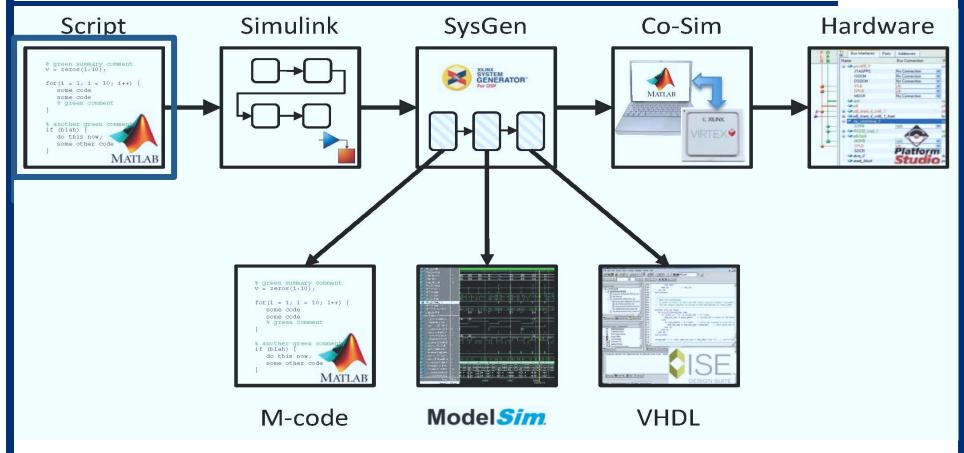

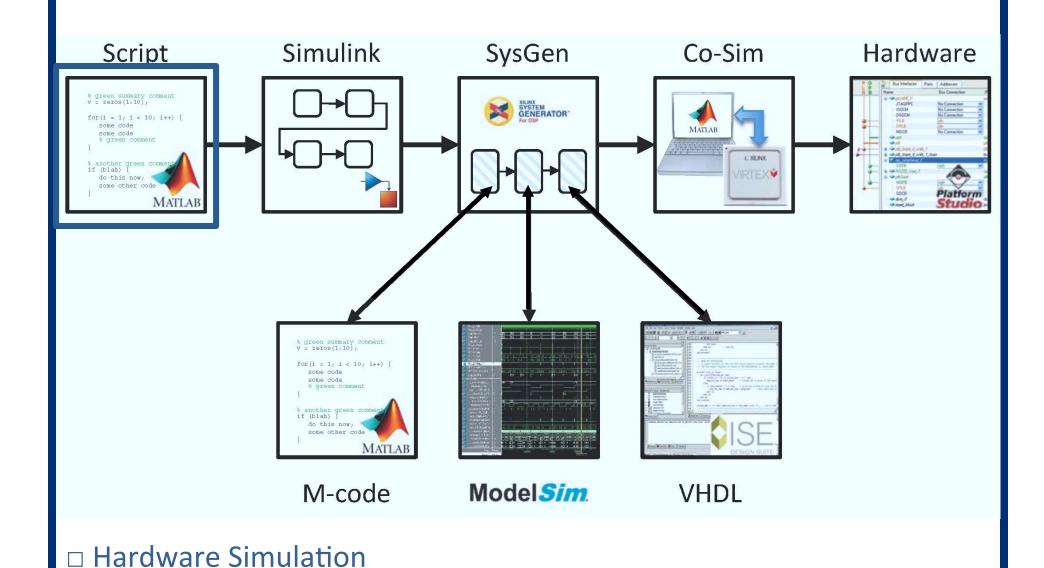

## Software/Hardware Design Flow

- □ Hardware Implementation

- Microblaze driven experiments

- On-board data generation and validation

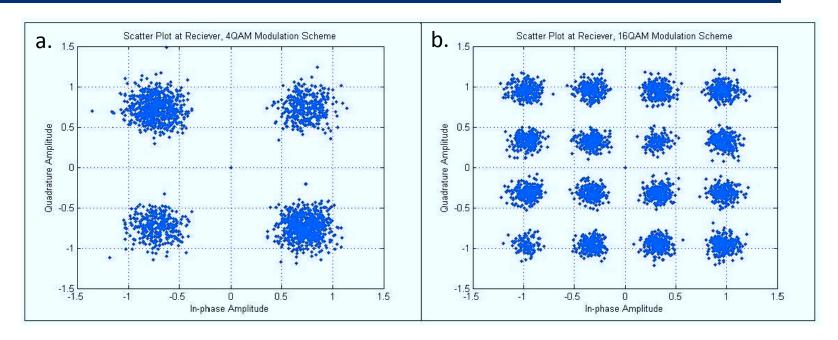

## Two Configurations of Coding and QAM

- AWGN channel

- Constellation mapping for:

- a. 4QAM mod 1/2 coding rate, SNR=15dB

- b. 16QAM mod 3/4 coding rate, SNR=20dB

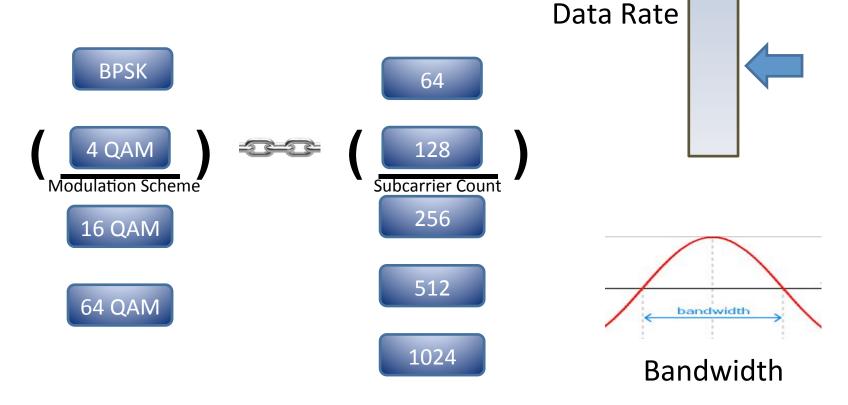

## What's the data rate?

#### Based of

- Communication standard

- Rates implemented

#### Conclusion

- Built Software Defined Communication Testbed (SDC)

- Described SDC's step by step design approach realizing PHY software implementation into hardware

- SDC provides flexibility and real-time speeds with its software interfaced hardware implementation

wireless.ece.drexel.edu/sdc

Questions?

## References

- [1] Chacko, James; Sahin, Cem; Nguyen, Danh; Pfeil, Doug; Kandasamy, Nagarajan; Dandekar, Kapil, "FPGA-based latency-insensitive OFDM pipeline for wireless research," High Performance Extreme Computing Conference (HPEC), 2014 IEEE, vol., no., pp.1,6, 9-11 Sept. 2014

- [2] ECMA-368: Standard: High rate ultra wideband PHY and MAC standard

- [3] IEEE 802.16: 2009 standard for local & metropolitan area networks part 16: Air interface for broadband wireless access systems.

- [4] IEEE 802.11: standard for wireless lan medium access control (mac) & physical layer (phy) specifications, 2012.

## OFDM Physical / Baseband layer

- Filter stage

- Enforcing BW limitations

- Modem stage

- Signal conditioning

- Most diverse

- Codec stage

- Frame/symbol conditioning

- Heavy computation

#### **PCIe Connection**

#### Gen 1 x8 PCIe connection provides the fastest data link

- Based on Microsoft's Speedy PCI Express design

- Provides DMA into FPGA RAM

- Measured write max BW: ~1.425 GB/s

- Measured read max BW: ~1.2 GB/s

- Still in development: Currently being integrated with other components of our system

### **Data Flow**

On-Board prototyping

Xilinx SDK/EDK+ ML605 HW + Radio frontend

### Hardware Platform

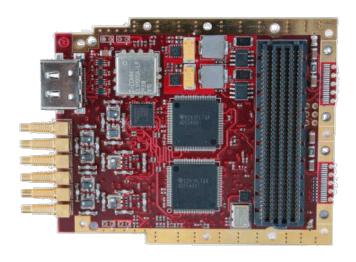

#### **Nutaq Radio420x**

- Frequency agility

- 300 MHz 3 GHz

- 20 MHz BW signals

- Programmable center frequency

#### **4DSP FMC110**

- Fast DAC / ADC 1Gsps

- 250 MHz BW signals

- UWB applications

## Orthogonal Frequency Division Multiplexing (OFDM)

- Encodes digital data unto multiple subcarrier frequencies

- Advantageous against inter symbol interference & frequency selective fading

- More sensitive to frequency and timing offset

- Simpler frequency equalization techniques compared to time domain

- Can increase performance through spatial diversity

- This area will be revisited later

- Baseband/Physical layer consists of components that works at different rates based on standard being implemented

## Generic OFDM Baseband Pipeline

#### Transmit Pipeline

## System Layout

## Software/Hardware Design Flow

# System Layout

## **Stall Propagation**

Stall caused by piloting block propagating backwards

# Software Defined Radio (SDR)

- Traditional radios are largely hardware based

- Physical components

- More difficult to modify

- Minimal flexibility

- SDRs can be defined as some or a lot of traditional hardware layers implemented through software