| Request    | Source    | State of<br>addressed<br>cache block | Type of cache action | Function and explanation                                                                                                                            |  |

|------------|-----------|--------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Read hit   | Processor | Shared or<br>modified                | Normal hit           | Read data in Jocal cache.                                                                                                                           |  |

| Read miss  | Processor | Invalid                              | Normal miss          | Place read miss on bus.                                                                                                                             |  |

| Read miss  | Processor | Shared                               | Replacement          | Address conflict miss: place read miss on bus.                                                                                                      |  |

| Read miss  | Processor | Modified                             | Replacement          | Address conflict miss: write-back block, then place read miss on bus.                                                                               |  |

| Write hit  | Processor | Modified                             | Normal hit           | Write data in local cache                                                                                                                           |  |

| Write hit  | Processor | Shared                               | Coherence            | Place invalidate on bus. These operations are often called upgrade or ownership misses, since they do not fetch the data but only change the state. |  |

| Write miss | Processor | Invalid                              | Nermal miss          | Place write miss on bus.                                                                                                                            |  |

| Write miss | Processor | Shared                               | Replacement          | Address conflict miss: place write miss on bus.                                                                                                     |  |

| Write miss | Processor | Modified                             | Replacement          | Address conflict miss: write-back block, then place write miss on bus.                                                                              |  |

| Read miss  | Bus       | Shared                               | No action            | Allow shared cache or memory to service read miss.                                                                                                  |  |

| Read miss  | Bus       | Modified                             | Coherence            | Attempt to share data: place cache block on bus and change state to shared.                                                                         |  |

| Invalidate | Bus       | Shared                               | Coherence            | Attempt to write shared block; invalidate the block.                                                                                                |  |

| Write miss | Bus       | Shared                               | Coherence            | Attempt to write shared block; invalidate the cache block.                                                                                          |  |

| Write miss | Bus       | Modified                             | Coherence            | Attempt to write block that is exclusive elsewhere; write-back the cache block and make its state invalid in the local cache.                       |  |

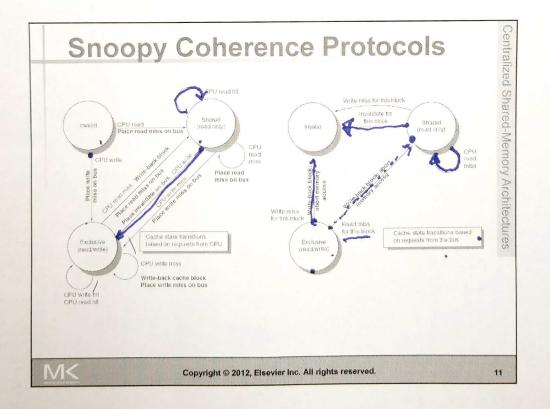

Involved.

Shored Plo.

Exclusive

Consider an SMP system with two processors A and B using the MSI snoopy cache coherence protocol. Assume we have memory location X addressed by the two processors. In the following table, you see the series of memory accesses by the two processors. Fill in the remainder of the table similarly to the first three rows.

| able similarly to | the first three rows.        | Invelora Wint   | ebock                        | 0               |

|-------------------|------------------------------|-----------------|------------------------------|-----------------|

| Processor         | Bus activity                 | Content of Proc | Contents of Proc             | Contents of mem |

| activity          | Bus detivity                 | A's cache       | B's cache                    | location X 4=0. |

| A writes X=2      | Windermis.                   | Exclusive x=2   | Mnoleta.                     | X=0. •          |

| B reads X         | Read miri B.x.               | Shared x=2      | Shored x=2.                  | ×=2             |

| A reads k.        |                              |                 | 1 1 2                        |                 |

| A writes X=3      | Invalidate.                  | Exclusive x:3   | Involid.                     |                 |

| B reads X         | Richmiss Bx<br>White Bouleyr | Shored x=3      | Shared x = 3                 | ×=3             |

| B writes X = 5    | Moleriale                    | Involved.       | Exclusive x=5                | X 2 3           |

| A writes <b>1</b> | Worde moss.                  | Exclusing X-57  | (nushed)                     | (K = 5°.)       |

| Y=1               | White back Bix.              | 1 X=1           | Mostrot                      | -120            |

| CAL               |                              | P. []           | Dead Miss<br>CZ<br>Des Miss. | 1)              |

| -                 |                              | J               | Bus.                         |                 |

|                   | DX                           | Mere.           | 000                          |                 |

|          |                | A            | B            | Men    |

|----------|----------------|--------------|--------------|--------|

| /        | _              | lopolia      | (Nuolid      | K=0    |

| Areed X. | read on the AK | Shored x = D | Involid.     | × = 0. |

| B read X | read mits B, X | Shord x=0    | Shared x = 0 | ×=0.   |

|          |                |              |              |        |

|          |                |              |              |        |

|          |                |              |              |        |